### **VCO & Synthesiser Design Sheet**

This sheet is a general purpose design sheet for LC VCOs and PLLs. The topic is fairly complicated and choices made in the VCO design affect the PLL loop filter settings.

Start by entering the VCO components assuming a Colpitts topology. Then, calculate the effective VCO Q Then, calculate the VCO phase noise profile, Then, the loop bandwidth and the integrated phase noise.

I will try to put some simulation results in soon, but at the moment this looks ok to me.

#### Chris Haji-Michael http://www.sunshadow.co.uk/chris.htm

$k_b := 1.388 \cdot 10^{-23} \frac{\text{joule}}{\text{K}}$   $T_{\text{K}} := 270 \cdot \text{K}$ fF :=  $10^{-15} \cdot \text{farad } \text{mW}_{\text{K}} := 10^{-3} \text{wat nH} := 10^{-9} \cdot \text{henry}$

VCO Details, QC is Q for the Capacitor which is assumed to be high compared to the L, The VCO is assumed to be Colpitts.

> f<sub>o</sub> := 1.76·10<sup>9</sup>·Hz <mark>Q<sub>C</sub> := 200</mark>

### VCO noise factor F

First calculate the noise factor (F) of the VCO transistor as defined by Rogers & Plett, Radio Freq Integrated Circuit Design (page 286), where **Rp** is the equivalent parallel resistance of the tuned circuit. Note that increasing the oscillator Q increases the noise floor.... not many people know that !!!

# The noise equations are from **Gray & Meyer** page 752 and 759 **Rb** is the transistor bias resistor (Rogers p 271), assume 1V drop at 1mA = 1kohm

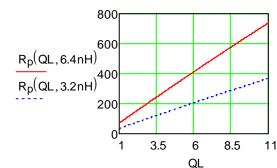

**Rp** is the effective parallel resistor of the VCO tuned circuit

and the higher this is, the higher the VCO wideband phase-noise, but the better close in phase noise.

$$\begin{split} \textbf{R}_{b} &\coloneqq 10000 \cdot \textbf{ohm} & i_{biasnoise} \coloneqq \sqrt{\frac{4 \cdot k_{b} \cdot T \cdot Hz}{R_{b}}} \\ \textbf{C}_{c}(L) &\coloneqq \frac{1}{\left(2 \cdot \textbf{p} \cdot f_{0}\right)^{2} L} & \textbf{R}_{C}(L) \coloneqq \frac{Q_{C}}{2 \cdot \textbf{p} \cdot f_{0} \cdot C(L)} & i_{biasnoise} = 1.224 \times 10^{-12} \cdot \textbf{amp} \\ \textbf{R}_{L}(\textbf{Q}_{L}, L) &\coloneqq \textbf{Q}_{L} \cdot L \cdot 2 \cdot \textbf{p} \cdot f_{0} & \textbf{R}_{p}(\textbf{Q}_{L}, L) \coloneqq \frac{1}{\frac{1}{R_{L}(\textbf{Q}_{L}, L)} + \frac{1}{R_{C}(L)}} & \textbf{C}(6.4\text{nH}) = 1 \times 10^{3} \cdot \text{fF}} \\ \textbf{R}_{p}(10, 6.4\text{nH}) = 674.036 \times 10^{0} \, \textbf{O} \end{split}$$

$$i_{\text{transistor}} := \sqrt{4 \cdot k_b \cdot T \cdot \frac{2}{3} \cdot g_m \cdot Hz}$$

? := 0.5

$g_m := 50 \frac{mA}{m}$

$$F(Q_{L},L) \coloneqq 1 + \frac{i_{biasnoise}^{2} \cdot R_{p}(Q_{L},L) \cdot ?}{k_{b} \cdot T \cdot Hz} + \frac{i_{transistor}^{2} \cdot R_{p}(Q_{L},L) \cdot (1-?)}{k_{b} \cdot T \cdot Hz}$$

$10\log(F(10, 6.4nH)) = 16.6$

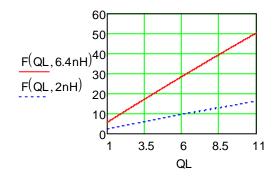

This plot on the right shows the effective noise figure of the VCO under different QL, and inductor values. It also takes into account the bias resistance and the transistor gm, but NOT the transistor noise. The noise figure can be surprisingly high, but this affects the **wideband** phase noise only (noisefloor).

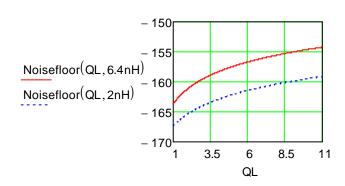

$$Noisefloor(Q_{L}, L) \coloneqq 10 \cdot log\left(2 \cdot T \cdot F(Q_{L}, L) \cdot k_{b} \cdot \frac{1}{joule}\right) + 30$$

Noisefloor(10, 6.4nH) = -154.6

Noise Floor in dBm

### **Oscillator Phase Noise**

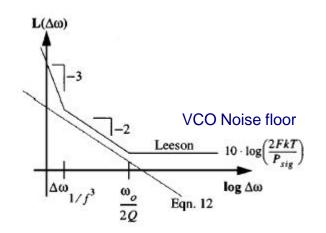

Now that we have the noisefloor, the phase noise can be found from Rogers & Plett, Radio Freq Integrated Circuit Design (page 286), equation 8.90 and adding the affect for noise floor but ignoring flicker noise.

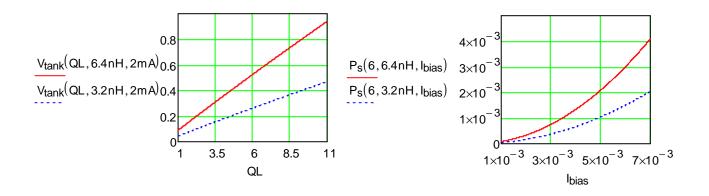

> Qt = Q of Oscillator tank Vtank = peak voltage swing in LC Ps = power in loop (assumed to be output power) PN is relative phase noise in dB

$$\mathsf{Q}_{T}\!\!\left(\mathsf{Q}_{L},L\right) \coloneqq \mathsf{R}_{p}\!\left(\mathsf{Q}_{L},L\right) \!\cdot \! \sqrt{\frac{\mathsf{C}(L)}{L}}$$

$Q_{T}(10, 6.4nH) = 9.524$

$V_{tank}(Q_{L}, L, I_{bias}) \coloneqq \frac{2}{p} \cdot I_{bias} \cdot R_{p}(Q_{L}, L)$

$\mathsf{P}_{\mathsf{S}}(\mathsf{Q}_{\mathsf{L}},\mathsf{L},\mathsf{I}_{\mathsf{bias}}) \coloneqq \frac{\mathsf{V}_{\mathsf{tank}}(\mathsf{Q}_{\mathsf{L}},\mathsf{L},\mathsf{I}_{\mathsf{bias}})^2}{2 \cdot \mathsf{R}_{\mathsf{p}}(\mathsf{Q}_{\mathsf{L}},\mathsf{L})}$

$V_{tank}(10, 6.4 nH, 1.5 mA) = 0.64 V$

$P_{s}(10, 6.4 nH, 1.5 mA) = 0.307 \cdot mW$

The VCO output power is assumed to be a quarter the power in the loop (Ps).

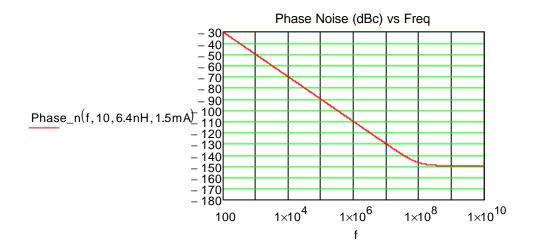

This calculates the phase noise accoding to the Leeson's equation assuming the phase-noise is dominated by the Q, i.e the noise slope is 20dB/decade. This plot will have the same wideband noise floor as specified above (in dBm) if Ps (above) is set to 4 \* 1mW.

The phase noise is in dBc

$$Phase_n(\mathbf{?} f, Q_L, L, I_{bias}) \coloneqq 10 \cdot log \left[ \left[ 1 + \left( \frac{f_o}{2 \cdot Q_T(Q_L, L) \cdot \mathbf{?} f} \right)^2 \right] \cdot \frac{2 F(Q_L, L) \cdot k_b \cdot T \cdot Hz}{P_s(Q_L, L, I_{bias})} \right]$$

Phase\_n(100·kHz, 10, 6.4nH, 1.5mA) = -90.2 Phase\_n(500·MHz, 10, 6.4nH, 1.5mA) = -149.3 dBc

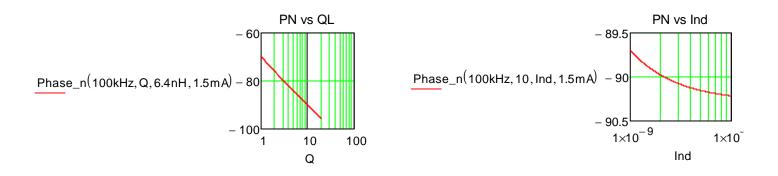

These plots show how the phase noise changes. There are only two ways to improve the phase noise, increase Q and increase current.

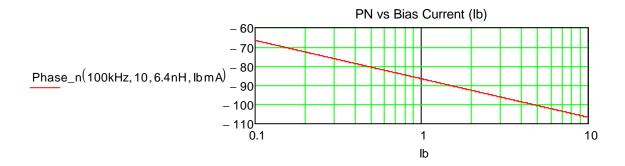

## Next, design the Synth for Minimum Phase Noise...

This part calculates the PLL in-band phase-noise in -dBc/Hz. **Fc** is designed to be the point where the VCO noise and the in-loop phase noise are the same as this will minimise the total Phase Noise out of the synth.

First we need to calculate the in-loop phase noise from **PNPD** (phase noise of the phase detector).

$$InLoopPN(PDPN, N) := PDPN + 10 \cdot log\left(\frac{prf}{Hz}\right) + 20 \log(N)$$

Noise from the phase detector dominates the in-band noise floor, given here. The noise is in dBc/Hz

InLoopPN(PDPN, 110) = -90.131 dBc/Hz

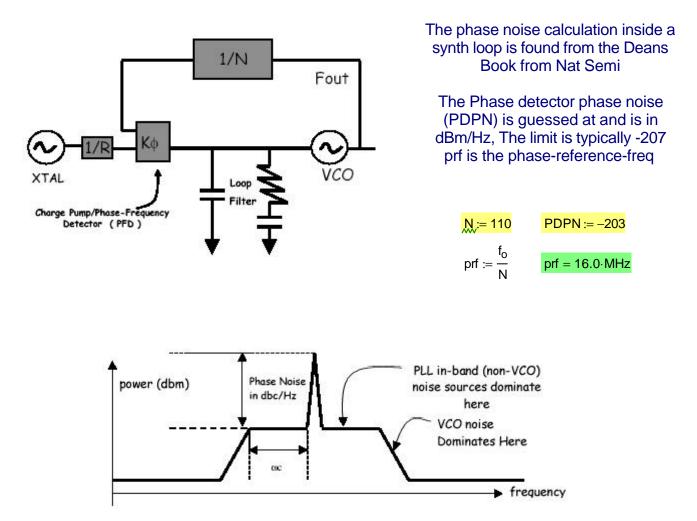

Then calculate Fc....

$$F_{c}(PNPD, N, Q_{L}, L, I_{bias}) \coloneqq \frac{1}{\frac{2 \cdot Q_{T}(Q_{L}, L)}{f_{o}} \cdot \sqrt{\frac{10^{\left(\frac{(InLoopPN(PNPD, N))}{10}\right)}{\left(\frac{2 \cdot F(Q_{L}, L) \cdot k_{b} \cdot T \cdot Hz}{P_{s}(Q_{L}, L, I_{bias})}\right)}} - 1$$

$F_{c}(-203, 110, 10, 6.4 \text{nH}, 1.5 \text{mA}) = 99.4317 \cdot \text{kHz}$

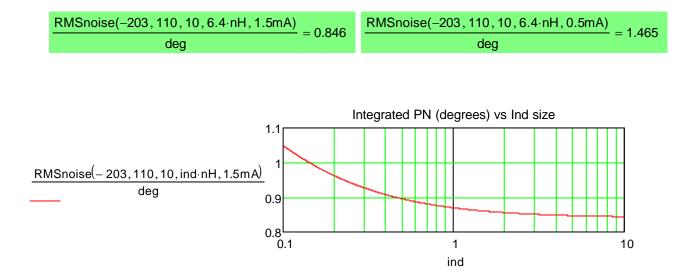

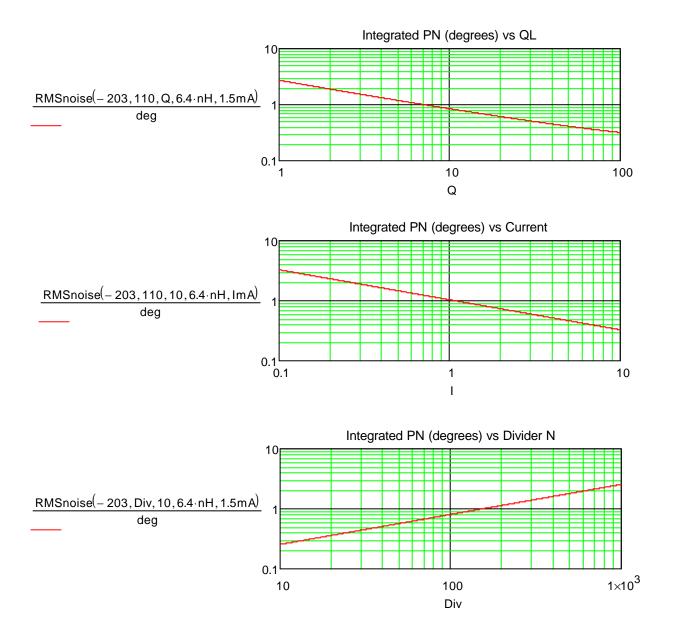

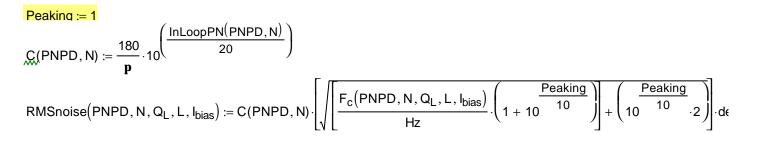

The integrated RMS phase noise in degrees is a very useful single-figure measure of performance and can be calculated using equations from page 50 of Deans book assuming a certain amount of peaking given in dB.

These results are interesting as they show that the total integrated-phase-noise, in a properly designed synth varies with CURRENT, Q, and N but not much with INDUCTANCE.

### High Current, High Q, Low N