## **Masters Thesis**

# Design of a Lossless Feedback Amplifier Using a 0.25µm CMOS Process

Chris Haji-Michael Aalborg University June 2004

#### PREFACE

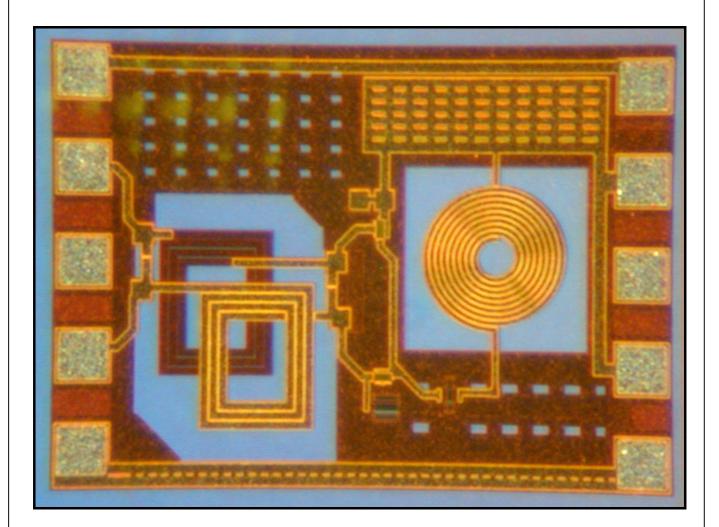

The Thesis investigates three circuit blocks for their suitability for fabrication on an IC. It investigates two types of RF Directional Coupler and combines one of these with a gain-block to build an amplifier topology referred to as a Lossless-Feedback or Norton Amplifier.

The design procedure for each of these circuit blocks is presented in the Thesis. A paper describing the design of one of the RF Directional Couplers has been written and submitted for publication. Test results for the Norton Amplifier look promising, but an IC fabrication error prevents direct comparison between the simulated and measured results and as a consequence it has not been possible to submit a paper on this. The IC is currently being re-fabricated but it has not been returned in time for testing. The second RF Directional Coupler was less successful, but using the information gathered during testing, this has been re-designed and I hope the University takes the opportunity to have this rebuilt, as it is an interesting and useful circuit that could see many applications.

A CD is attached on the back page of this Thesis that contains an electronic copy of this document with hyperlinks to many of the references. It also includes the LabVIEW scripts, MathCAD files, ADS simulation files, results data and Cadence layout files used in this Thesis.

I would like to take this opportunity to thank the staff in the RISC group at Aalborg University for allowing me to return to study and to give me this opportunity to learn the techniques for designing and testing an RFIC. I am very grateful for this and for all their help, especially the PhD students who answered all my many questions. I would specifically like to thank my supervisor Ole Kiel Jensen for his invaluable comments, and to RFMD for the use of one of their machines that I needed during the testing.

The fabrication process used in this Thesis is from UMC and they have demanded confidentiality of their process. As a consequence this Thesis should not be made available to unauthorized readers.

Thank you,

Chris Haji-Michael chm@sunshadow.co.uk

## TABLE OF CONTENTS

| 1   | INTRODU              | JCTION                                    | 1      |

|-----|----------------------|-------------------------------------------|--------|

| 1.1 | Project              | Outline                                   | 1      |

| 1.2 |                      | on and Explanation of terms               |        |

|     |                      | blifier Linearity                         |        |

|     | 2.2 Thire            | d-Order Intercept Point                   | 4      |

|     | 2.3 1dB              | Compression Point                         | 5      |

| 1.2 | 2.4 AM               | to PM conversion                          | 5      |

|     |                      | pility                                    |        |

|     |                      | pility Circles                            |        |

|     |                      | ٦                                         |        |

| 1.2 | 2.8 Nois             | se Figure                                 | 7      |

| 1.3 | Types o              | f Lossless Feedback Amplifier             | 8      |

| 1.4 | Amplifie             | er Performance Considerations1            | 0      |

| 1.4 |                      | ulation Results of an Ideal LF Amplifier1 |        |

| 1.5 | Project              | Goals1                                    | 3      |

|     |                      |                                           |        |

| 2   | NORTON               | I AMPLIFIER DESIGN1                       | 5      |

| 2.1 | Overall              | Design Philosophy1                        | 5      |

| 2.2 | Design               | of RF Directional Coupler1                | 5      |

|     |                      | nchline Coupler                           |        |

|     | -                    | Branchline Coupler on the IC              |        |

|     |                      | nsmission Line Coupler                    |        |

|     | -                    | nsformer Coupler                          |        |

|     |                      | clusion on Coupler Options                |        |

| 2.3 | Desian               | of Gain-Block                             | 6      |

|     |                      | jle FET Gain-Block                        |        |

|     |                      | iple Transistor Gain-Block                |        |

|     |                      | PET Gain-Block                            |        |

|     |                      | ition of Noise Optimization Inductor      |        |

| 24  | Comple               | ta Amplifiar Dasian 2                     | 4      |

| 2.4 |                      | te Amplifier Design                       |        |

|     | 4.1 Frec<br>4.2 Disc | quency Choice                             | ן<br>ר |

|     |                      | rete Component Coupler at 2.5GHz          |        |

| ۷.4 | +.5 COII             |                                           | 3      |

| 3   | DESIGN               | OF THE INTEGRATED CIRCUIT                 | 7      |

| 3.1 | IC Cons              | struction3                                | 7      |

| 3.2 | Suh ∆ee              | semblies3                                 | 8      |

|     |                      | crete Component Coupler                   |        |

|     |                      | sformer Coupler                           |        |

|     |                      | n-Block                                   |        |

| 0.1 | Sull                 |                                           | 5      |

|                     | Passive Components                    |       |

|---------------------|---------------------------------------|-------|

| 3.3.1               |                                       |       |

| 3.3.2               | Resistors                             | 52    |

| - · -               |                                       |       |

| 3.4 F               | Probe Calibrator                      | 53    |

|                     |                                       |       |

| 4 DE                | SIGN OF THE NORTON AMPLIFIER          | 55    |

|                     | Demoural .                            |       |

|                     | General                               |       |

| 4.1.1<br>4.1.2      |                                       |       |

| 4.1.2               |                                       |       |

| 4.1.5               |                                       |       |

| с т <b>с</b>        |                                       | 64    |

| 5 TE                | ST RESULTS                            |       |

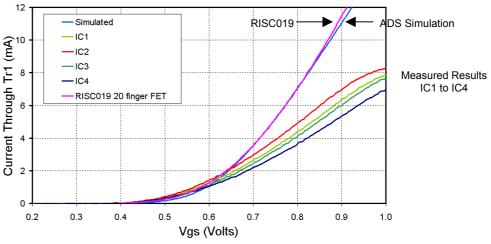

| 5.1 A               | Analysis of Fabricated IC             | 61    |

| 5.1.1               | •                                     |       |

| 5.1.2               |                                       |       |

| 5.1.3               |                                       |       |

|                     |                                       |       |

| 5.2 3               | β2μm Capacitor                        | 63    |

| <b>5</b> 0 <b>5</b> |                                       |       |

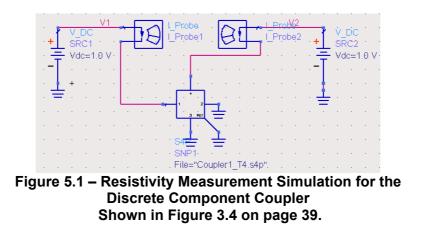

| 5.3 C               | Discrete Component Coupler            | 64    |

| 5.4 T               | Fransformer Coupler                   | 65    |

| 0.4 1               |                                       |       |

| 5.5 A               | Amplifier                             | 68    |

| 5.5.1               |                                       |       |

| 5.5.2               | Amplifier Results                     | 69    |

|                     |                                       |       |

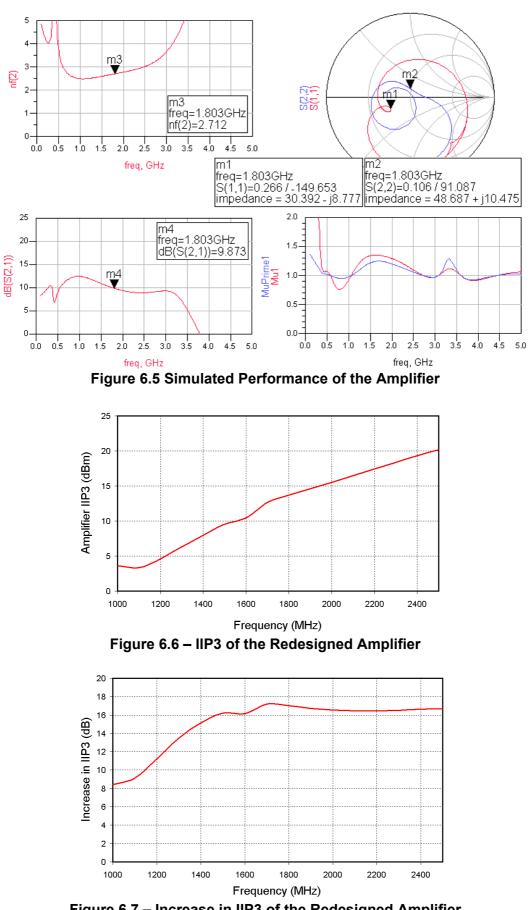

| 6 CC                | ONCLUSIONS AND CIRCUIT REDESIGN       | 73    |

|                     |                                       |       |

| 6.1 C               | Conclusions from Measured Results     | 73    |

|                     |                                       |       |

|                     | Amplifier Redesign                    |       |

| 6.2.1               |                                       |       |

| 6.2.2               | · · · · · · · · · · · · · · · · · · · |       |

| 6.2.3<br>6.2.4      | 0                                     |       |

| 0.2.4               |                                       |       |

| 6.3 T               | Fransformer Coupler Redesign          | 79    |

|                     |                                       |       |

| DEEE                | RENCES                                | 83    |

|                     |                                       | 05    |

|                     |                                       |       |

| APPE                | NDIX A MATHCAD SHEETS                 | 85    |

|                     |                                       |       |

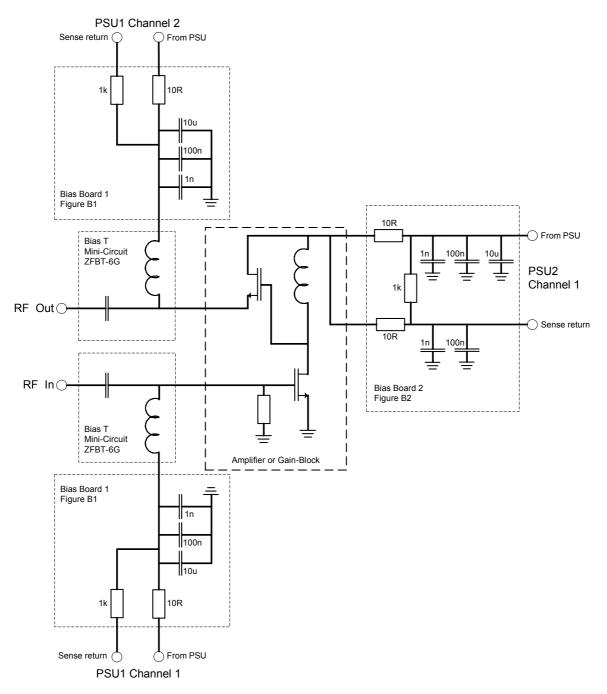

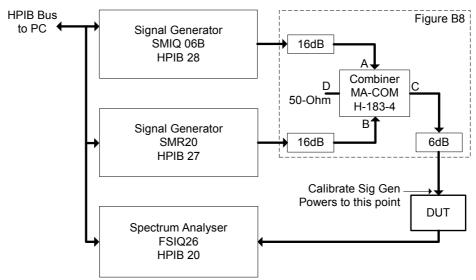

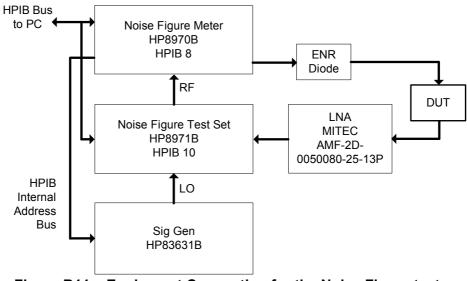

| APPE                | NDIX B TEST SYSTEM                    | 97    |

|                     |                                       |       |

|                     | NDIX C PHOTOGRAPHIC IMAGES            | 105   |

|                     |                                       |       |

|                     |                                       | 4.6.6 |

| APPE                | NDIX D RESULTS DATA                   | 109   |

## 1 INTRODUCTION

## 1.1 Project Outline

The aim of this project is to investigate and design a type of amplifier referred to as lossless feedback amplifier with regard to its suitability for use in an integrated circuit design.

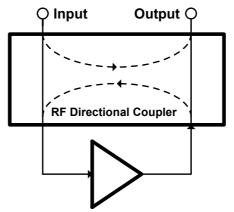

The use of feedback around an amplifier has been used for many years to control and improve amplifier performance. Several factors are known to change when feedback is used, of which linearity and noise-figure are the two main factors investigated as part of this report. The normal method of adding feedback to an amplifier is to use resistive components, but these add noise and degrade the amplifier noise figure. It is however possible to employ reactive components in the feedback path and to enjoy the advantages of improved linearity but with a minimal degradation to the amplifier noise figure. Such an amplifier was first proposed and patented by D. Norton [1] of the Anzac Corporation, with the basic structure of this type of amplifier shown in Figure 1.1. Amplifiers of this type are referred to as Norton amplifiers, and were sold operating to typically 200MHz.

It is the intention of this project to design and build a Norton amplifier that operates at 2GHz on a CMOS process. This type of amplifier has to the authors knowledge not been built on an IC before and there are no published papers to give guidance on the approach that should be taken. In addition, a suitable coupler required to provide the necessary coupling has also not been built, although the design of a 3dB hybrid was published in March 2003 by Frye [2] and is used as a starting point for this design.

Figure 1.1 – Block Diagram of Lossless Feedback Amplifier Using an RF directional coupler as the feedback path.

This thesis starts by investigating suitable couplers; with the design choices for these and the gain-block presented in Chapter 2. The IC construction is explained in Chapter 3 and this also includes information on the simulation and layout of the passive components.

Two couplers and the Norton amplifier were selected for fabrication and the test results for these are presented in Chapter 5. The test results show that the amplifier and one of the couplers is successful and show good correlation between the simulated and measured results. The results for the second coupler do not agree with the simulations and this is investigated as part of Chapter 5. An updated design for the second coupler is presented in Chapter 6.

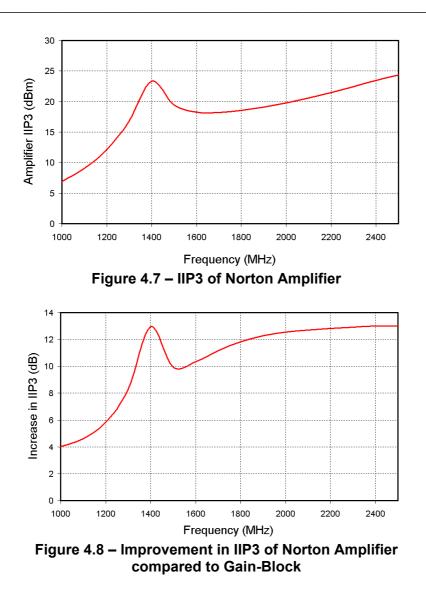

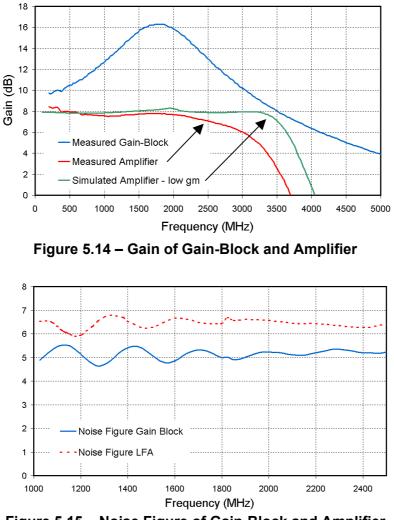

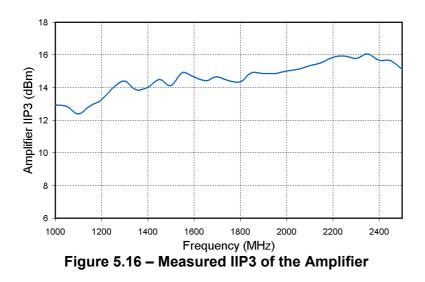

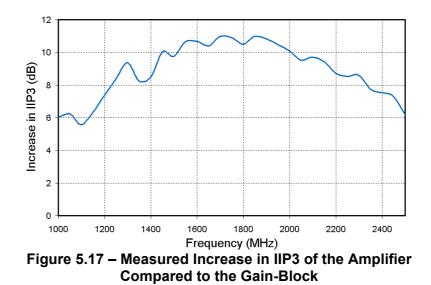

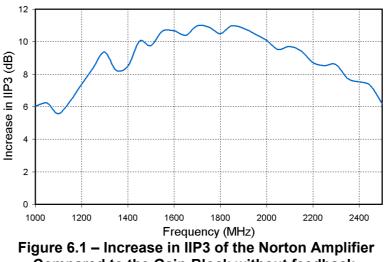

The results in Chapter 5 (Figure 5.13) show that the amplifier achieves a 10dB increase in IIP3 over the frequency band 1.5 to 2GHz and this is the first time that such an amplifier has been demonstrated. An updated amplifier with biasing is presented in Chapter 6.

## 1.2 Definition and Explanation of terms

## 1.2.1 Amplifier Linearity

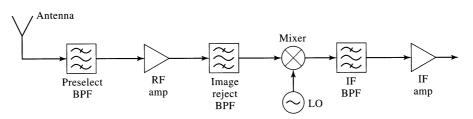

A receiver picks up a variety of signals from the antenna at different power levels and frequencies and in amongst these is the wanted signal. The receiver must be able to amplify and demodulate this signal, usually at a very low power level in the presence of the other signals that are often at much higher power levels.

Non-linearities in the receiver chain can prevent this from happening. Mixing affects allow two unwanted frequencies to mix together to generate a number of spurious signals. If one of these unwanted spurious signals falls at the frequency of interest, it will affect the demodulator performance and this will result in a degraded signal to noise ratio.

A clear way to explain this affect is mathematically. The mixing products generated by two signals can be expressed as a Taylor series expansion in terms of the input voltage  $v_i$  and where  $v_o$  is the output voltage. In this analysis the input voltage is made up of two closely spaced frequencies  $\omega_1$  and  $\omega_2$  as follows.

$$v_i = V_0 \cdot \left(\cos \omega_1 t + \cos \omega_2 t\right)$$

The output voltage can be expressed as follows after expansion of the Taylor Series:

$$v_0 = \alpha_0 + \alpha_1 V_0 (\cos \omega_1 t + \cos \omega_2 t) + \alpha_2 V_0^2 (\cos \omega_1 t + \cos \omega_2 t)^2 + \alpha_3 V_0^3 (\cos \omega_1 t + \cos \omega_2 t)^3 + \dots$$

Which becomes:

$$\begin{split} v_0 &= \alpha_0 + \alpha_1 V_0 \cos \omega_1 t + \alpha_2 V_0 \cos \omega_2 t \\ &+ \frac{1}{2} \alpha_2 V_0^2 \left( 1 + \cos 2\omega_1 t \right) + \frac{1}{2} \alpha_2 V_0^2 \left( 1 + \cos 2\omega_2 t \right) \\ &+ \alpha_2 V_0^2 \cos(\omega_1 - \omega_2) t + \alpha_2 V_0^2 \cos(\omega_1 + \omega_2) t \\ &+ \alpha_3 V_0^3 \left( \frac{3}{4} \cos \omega_1 t + \frac{1}{4} \cos 3\omega_1 t \right) + \alpha_3 V_0^3 \left( \frac{3}{4} \cos \omega_2 t + \frac{1}{4} \cos 3\omega_2 t \right) \\ &+ \alpha_3 V_0^3 \left( \frac{3}{2} \cos \omega_2 t + \frac{3}{4} \cos(2\omega_1 - \omega_2) t + \frac{3}{4} \cos(2\omega_1 + \omega_2) t \right) \\ &+ \alpha_3 V_0^3 \left( \frac{3}{2} \cos \omega_1 t + \frac{3}{4} \cos(2\omega_2 - \omega_1) t + \frac{3}{4} \cos(2\omega_2 + \omega_1) t \right) + \dots \end{split}$$

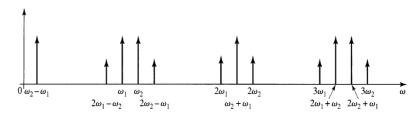

The combination of  $\omega_1$  and  $\omega_2$  are called the *intermodulation products*. The  $V_0^2$  terms from the above equation is referred to as the *second order term*, of which there are four:  $2\omega_1$ ,  $2\omega_2$ ,  $\omega_1 - \omega_2$  and  $\omega_1 + \omega_2$ . A simple way to categorize these is to define the output as  $m\omega_1 + n\omega_2$ , where the order is defined as |m| + |n|. The second order frequency products are listed in Table 1.1, and in a similar way the third order products can be listed for  $V_0^3$  terms; of which there are six. These terms are listed in Table 1.2.

All the products generated by an amplifier are undesirable, however the spurious signals that are generated some distance away from the wanted signal can be easily filtered out before the mixer and should present no great challenge in the receiver design. The products that present the greatest cause for concern are the adjacent spurious signals  $2\omega_1 - \omega_2$  and  $2\omega_2 - \omega_1$ , as these are too close to the wanted signal to be filtered out and can only be controlled by designing the amplifier to be sufficiently linear.

| Order | т | п  | Spurious              | Description                         |

|-------|---|----|-----------------------|-------------------------------------|

| 2     | 2 | 0  | $2\omega_1$           | Second harmonic of $\omega_{\rm l}$ |

| 2     | 0 | 2  | $2\omega_2$           | Second harmonic of $\omega_2$       |

| 2     | 1 | -1 | $\omega_1 - \omega_2$ | Difference                          |

| 2     | 1 | 1  | $\omega_1 + \omega_2$ | Sum                                 |

Table 1.1 - Second Order Intermodulation Terms

| Order | т  | п  | Spurious               | Description                        |  |  |

|-------|----|----|------------------------|------------------------------------|--|--|

| 3     | 3  | 0  | $3\omega_1$            | Third harmonic of $\omega_{\rm l}$ |  |  |

| 3     | 0  | 3  | $3\omega_2$            | Third harmonic of $\omega_2$       |  |  |

| 3     | 2  | -1 | $2\omega_1 - \omega_2$ | Low side adjacent spurious         |  |  |

| 3     | -1 | 2  | $2\omega_2 - \omega_1$ | High side adjacent spurious        |  |  |

| 3     | 2  | 1  | $2\omega_1 + \omega_2$ |                                    |  |  |

| 3     | 1  | 2  | $2\omega_2 + \omega_1$ |                                    |  |  |

Table 1.2 – Third Order Intermodulation Terms

A spectrum showing only the second and third-order terms can be seen in Figure 1.2, this shows that most mixing products are some distance away from  $\omega_1$  and  $\omega_2$ . A typical receiver is shown in Figure 1.3, one of the advantages for putting a filter between the first amplifier and the mixer is to remove these unwanted mixing products. This filter however cannot remove the adjacent channel spurious signals and it is an important specification for the LNA design is to be sufficiently linear so as not to generate these unwanted spurious signals in the operating environment.

Figure 1.2 – Output Spectrum of 2nd and 3<sup>rd</sup>-order Intermodulation Products [3]

Figure 1.3 – Typical Receiver Topology [3]

## 1.2.2 Third-Order Intercept Point

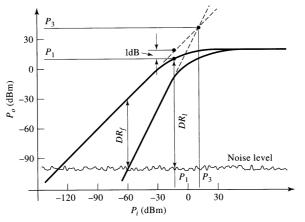

The LNA linearity is conveniently measured using the *third-order Intercept Point*. The mixing product from two unwanted signals increases as a cube of the input power. For small signals the third-order intermodulation products will be small but will increase quickly as the input power increases. This effect can be seen in Figure 1.4 where the first and third-order output products are plotted against the input power. The scales on both axes are logarithmic and it can be seen from this graph that this device shows a gain of 30dB and that the fundamental signal increases linearly until the output power compresses at 20dBm.

Figure 1.4 – Third Order Intercept Diagram [3]

The third order products increase at a slope of three, since the fundamental and third order products have different slopes they intersect at a point that is referred to as the *Third Order Intercept Point*, shown as P3 in Figure 1.4. Either the input or output intercept points are acceptable to define the amplifier linearity and it is easy to switch between the two points by adding or subtracting the amplifier gain.

To maintain consistency and simplicity in comparing the different amplifiers, this report uses only the *input* third order intercept point, written as IIP3, but which may also be written as TOIi. This report uses IIP3 throughout and allows a direct comparison with published literature [please refer to chapter 1.5].

The unwanted frequencies used for this measurement are typically between  $\pm 200$ kHz and  $\pm 2$  MHz from the wanted signal. As an example for the GSM spec [4] the unwanted intermodulation frequencies for GSM900 are set to  $\pm 800$ kHz and  $\pm 1600$ kHz, at -49dBm. These unwanted signals must not degrade the performance of the receiver demodulating the wanted signal, which is set to 3dB above the reference sensitivity to -101dBm. Assuming the unwanted spurious level needs to be 6dB below the wanted signal to have little influence on the receiver BER, i.e. a power level of less than -107dBm, then the IIP3 of the receiver can be calculated from the equation below.

$$IIP3 = UnwantedSignalLevel + \frac{1}{2}(UnwantedSignalLevel - SpuriousLevel)$$

using values from the GSM spec:

$$IIP3 = -49dBm + \frac{1}{2}(-49dBm - -107dBm)$$

this gives an:

$$IIP3 = -20dBm$$

This equation gives a good insight as to the benefit that may be obtained by an improvement in the receiver IIP3. A 10dB improvement in the IIP3 indicates that the spurious signal levels will have fallen by 20dB.

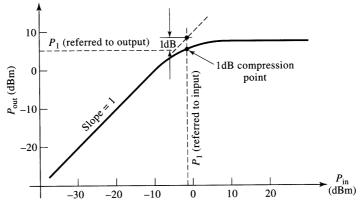

## 1.2.3 1dB Compression Point

Another measure of linearity is the 1dB compression point, which is measured using a single input CW frequency. The response of a typical amplifier is shown in Figure 1.5; for an ideal linear amplifier a plot of the output power versus the input power is a straight line with a slope of unity. In this figure the gain of the amplifier is 10dB but as the input power increase the output saturates reducing the gain. The output power at which the gain drops 1dB below the expected value is referred to as the 1dB compression point and is always referenced to the output of the amplifier, it is written as P1dB.

Figure 1.5 – 1dB Compression Point [3]

## 1.2.4 AM to PM conversion

When an amplifier is driven close to its compression point, a change in the amplitude of the input signal can result in a change in the phase. This is known as the AM to PM conversion and needs to be seriously considered with RF systems that transmit or receive certain types of modulation, and is another description of amplifier linearity.

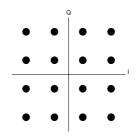

The effect is most important when the modulation has both an amplitude and phase component for example with QAM signals. A 16-bit QAM constellation is shown in Figure 1.6 and has 16 points, each with a unique amplitude and phase. If this signal is amplified using an amplifier with a poor AM-PM conversion then the amplifier will distort the signal such that the outer constellation points have a different phase shift compared to the inner constellation points and this will result in a degraded system BER and increased output harmonics.

Figure 1.6 – 16-QAM Signal Constellation

#### 1.2.5 Stability

Adding feedback to an amplifier increases the chance that the amplifier will become unstable, as stability depends on the gain and phase of *all* the parts in the circuit. The standard method of assessing the stability of an amplifier is to calculate the *Rollet's* stability measure using the amplifier S-parameter data. The *Rollet's* measure is calculated as shown below and two conditions need to be met for the amplifier to be considered unconditionally stable.

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2 \cdot |S_{12}S_{21}|} > 1$$

$$\left|\Delta\right| = \left|S_{11}S_{22} - S_{12}S_{21}\right| < 1$$

Unconditional stability is when the circuit is stable and will not oscillate under *all* load and source impedances. The stability factor needs to be calculated at many frequencies over a wide frequency band and not just over the amplifier band of interest. An oscillation at *any* frequency is of concern and will degrade the performance of the amplifier usually influencing the amplifier noise figure and the gain. The typical bandwidth to apply this measure to is from a few megahertz up to  $F_T/2$  frequency of the transistor. For the UMC process, stability is calculated up to 10GHz.

Other measures of stability that has become popular over recent years are  $\mu$  and  $\mu'$ , as defined Edward and Sinsky [5]. These are the geometrically derived stability factors where  $\mu$  is the stability factor for the load, and  $\mu'$  is the stability factor for the source. These values give a simple measure of the distances from the center of the Smith chart to the nearest point of instability as shown using stability circles. Both of these values need to be greater than 1 for unconditional stability and the value given are directly proportional to degree of instability.

Part of the motivation behind the Edward and Sinsky method is that the Rollet's measure of stability is more complex than presented above. Stability requires K>1, and *any one* of the following conditions to apply, of which the most commonly used is  $|\Delta|$ .

$$B_{1} = 1 + |S_{11}|^{2} - |S_{22}|^{2} - |\Delta|^{2} > 0$$

$$B_{2} = 1 - |S_{11}|^{2} + |S_{22}|^{2} - |\Delta|^{2} > 0$$

$$|\Delta| = |S_{11}S_{22} - S_{12}S_{21}| < 1$$

$$1 - |S_{11}|^{2} > |S_{12}S_{21}|$$

$$1 - |S_{22}|^{2} > |S_{12}S_{21}|.$$

This makes the Rollet's analysis complex and difficult to appreciate how much margin there is in the design of a circuit. The stability measures of  $\mu$  and  $\mu'$  are easily calculated as shown below and both parts need to be >1 for unconditional stability. Both the Rollet's and  $\mu \& \mu'$  indicators are all used in this report.

$$\mu = \frac{1 - |S_{11}|^2}{|S_{22} - S_{11}^* \cdot \Delta| + |S_{21} \cdot S_{12}|}$$

$$\mu' = \frac{1 - |S_{22}|^2}{|S_{11} - S_{22}^* \cdot \Delta| + |S_{21} \cdot S_{12}|}$$

## 1.2.6 Stability Circles

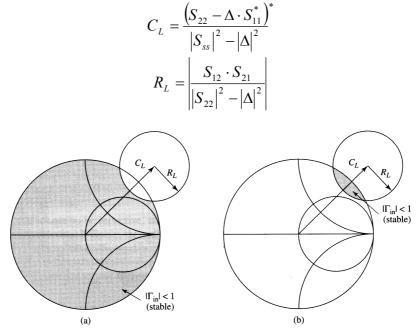

Stability Circles are a graphical method of showing the stability of an amplifier. The derivation of these circuits is complex and the reader is referred to Pozar [3] for more information. Stability circles are normally calculated for both the load (output) and source (input) impedances and show the impedances that are likely to cause the amplifier to become unstable.

The center and radius of these circles are calculated at each frequency according to the following equations. For simplicity these are given for the load impedance, but similar equations can be found for the source impedance. This circle can be plotted on a Smith chart as shown in Figure 1.7.

Figure 1.7 – Stability Circles [3]

If the amplifier is unconditionally stable, the stability circles must be completely outside or totally enclose the smith chart. One difficulty with interpreting stability circles is working out which region shows the stable impedances and which is the unstable region, as either condition shown in Figure 1.7 may be correct. There are two ways to do this, the first is to calculate  $|S_{11}|$  and this is shown in Figure 1.7(a) is with  $|S_{11}| < 1$  and Figure 1.7(b) is with  $|S_{11}| > 1$ . The second method is to use  $\mu \& \mu'$  as the indicators.

## 1.2.7 Gain

The value of gain used throughout this report is  $|S_{21}|^2$  which assumes the same port impedance on both the input and output ports.

## 1.2.8 Noise Figure

The amplifier adds noise to the signal such that the noise figure of the amplifier is a ratio of the input and output signals and noise powers as follows. This report expresses the Noise figure in dBs;  $F(dB) = 10 \cdot Log(F)$ .

## 1.3 Types of Lossless Feedback Amplifier

D Norton of the Anzac Corporation patented the first lossless-feedback amplifier in 1971 [1][6]. He proposed that a directional coupler could be used in the feedback path around the transistor and thereby improved the amplifier linearity but without substantially affecting the input and output impedance and the amplifier noise figure. This group of amplifiers is collectively referred to as *Norton* amplifiers.

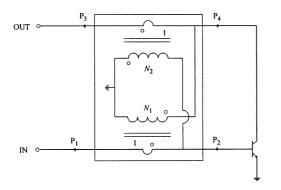

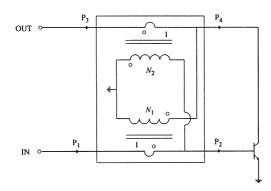

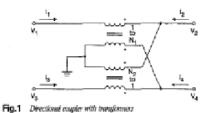

In the patented configuration shown in Figure 1.8, two independent transformers are used to form a single directional coupler that has zero phase-shift between ports P4 and P2. Some of the output power from the transistor at P4 feeds back to the input port P2 at zero-phase thus creating a feedback path in much the same way as a resistive element could be used. The advantage is this mechanism should not introduce additional noise power that a corresponding resistor would introduce and should therefore not degrade the amplifier noise figure. In addition, the use of directional couplers allows the feedback mechanism to work without influencing the input or output impedance and these should remain unchanged.

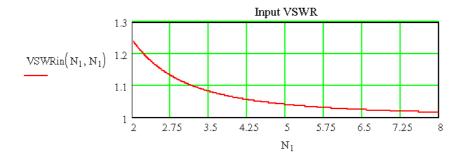

With this topology for optimum performance, the base and collector impedance of the transistor should be the same as the impedance of the IN and OUT ports, so for a 50-Ohm amplifier the base and collector impedances should look like 50-Ohm.

Figure 1.8 – D Norton Lossless Feedback Amplifier [6]

It is interesting to note with this circuit that some of the input power passes directly to the output port via the directional coupler and we should see some output power even if the transistor were not fitted. As the coupler is reciprocal the reverse of this must happen and a proportion of any power in the output port will be coupled directly to the input. This indicates that the reverse isolation of this type of amplifier is limited to coupling level of the coupler.

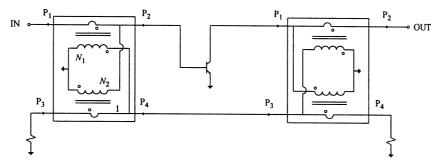

For some applications this may be a problem and this was solved in 1977 by Q-bit [7] using two directional-couplers instead of one. The topology for this amplifier is shown in Figure 1.9; in this arrangement any RF power incident on the output port is split between the transistor and a terminating load on P4. The reverse isolation of this topology is that of the transistor itself plus any losses associated with the couplers. The disadvantage is that there is slightly less output power, as part of the input power in the original design would contribute to the output power, in addition there is also increased losses using two couplers and the circuit is more complex.

Figure 1.9 - Q-Bit Norton Amplifier [6]

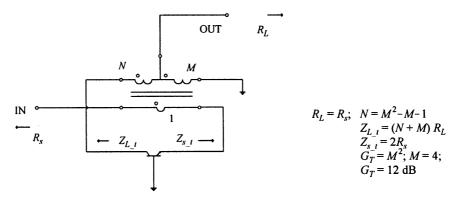

In 1975, D. Norton and A. Podel patented [8] another topology that uses a wound transformer in place of the directional couplers and works using a single transistor amplifier stage. In this circuit shown in Figure 1.10, for correct operation the input impedance of the transistor should approximate a short circuit, while the output impedance should look like an open circuit.

Figure 1.10 - Transformer Wound Norton Amplifier [6]

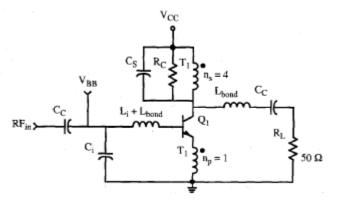

A different class of feedback amplifiers is the *transformer feedback amplifier* by Long and Copeland in 1995 [9]. The circuit they proposed is shown Figure 1.11 and uses a transformer with a 1 to 4 winding ratio to replace the collector and emitter impedances normally used in amplifier design. The design presented is tuned for narrow-band operation with the addition of a collector capacitor and has a number of matching off-chip components.

A 1.9GHz LNA was built using this topology on a 0.8um silicon process and biased at 1.9V, 2mA. It showed a gain of 9.5dB with a 2.1dB NF and an IIP3 of –3dBm. The IIP3 was estimated to be 10dB better than would have been obtained from a non-transformer design.

Figure 1.11 – Transformer Feedback Amplifier [9]

The final class of lossless amplifier is the *op-amp* type of amplifier, an example of which is shown in Figure 1.12. In the paper by Nozal [10], the author proposed using series-capacitative feedback to produce a broadband MMIC amplifier built using a PHEMT GaAs process that achieves less than 1.4dB noise figure up to 5GHz and 25dB of gain up to 7GHz, although no mention was made of the amplifier linearity or stability.

The phase of the feedback circuit is controlled with additional resistors in parallel with the feedback capacitors. It is possible to achieve a similar topology with inductive feedback but perhaps with less control and narrower bandwidth. Such a topology with inductive feedback on an IC has not been found in the literature. This is the only published example of this type of amplifier.

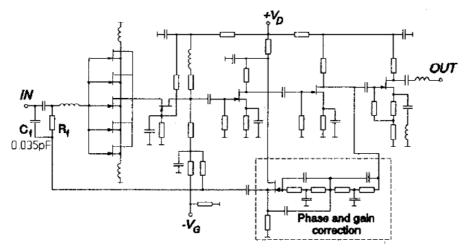

Figure 1.12 – RF Op-Amp lossless feedback amplifier [10]

## **1.4 Amplifier Performance Considerations**

There are several amplifier performance measures that are affected by adding feedback to an amplifier. One of which is amplifier linearity, specifically the third-order-intercept point, but also to a lesser extent the 1dB compression point. Table 1.3 summaries the amplifier factors that are likely to change when feedback is added.

The most obvious advantage to adding feedback around an amplifier is that feedback now controls the gain of that amplifier. This is a useful feature if the amplifier gain is found to vary because of processing variations or with temperature or supply voltage. Adding feedback controls and defines the gain, but of course is subject to tolerances of its own.

If the gain of the amplifier is to be dominated by the feedback components, then the gain of the gain-block needs to be substantially higher, preferably more than 10dB higher than the gain of the required final amplifier design. For example if an amplifier of 10dB gain is required, then the gain-block should have a gain of at least 20dB before feedback is added.

A large motivation for adding feedback to an amplifier is to improve the amplifier linearity, specifically the IIP3. Simulations of an ideal amplifier shown in section 1.4.1, Figure 1.15 shows that the IIP3 increases in proportion to the gain in the gain-block.

A second measure of amplifier linearity, the 1dB compression point is unlikely to change much when feedback is added as this is dominated by the supply voltage and the corresponding output peak-to-peak voltage swing. However a small improvement should be expected as the 1dB compression curve changes from a soft curve to a hard curve with the feedback mechanism keeping the amplifier linear right up to the point when the amplifier output clips.

| Linearity                       | The output signal from an amplifier should ideally be a perfect amplification of the input signal without distortion and harmonics.                                                                                                                |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | Feedback improves the amplifier linearity and is the primary motivation for investigating this type of amplifier.                                                                                                                                  |

| Gain &<br>Bandwidth             | Feedback reduces the gain and flattens the bandwidth of the amplifier.                                                                                                                                                                             |

| Input &<br>Output<br>Impedances | When feedback is added to an amplifier this will change both input and output impedances. This may be desirable depending on the application. If directional couplers are used in the feedback path then these impedance changes can be minimized. |

| Circuit<br>Complexity           | Feedback makes the circuit more complex and adds cost.                                                                                                                                                                                             |

| Stability                       | The amplifier is much more likely to become unstable and produce unwanted oscillations.                                                                                                                                                            |

| Noise Figure                    | Conventional resistive feedback adds noise to the output and increases the amplifier Noise Figure. Lossless feedback using reactive components should minimize the added noise.                                                                    |

Table 1.3 – Summary of Amplifier factors that change with feedback

The feedback from the RF directional coupler should not contribute to the NF of the amplifier other than with additional forward path losses that need to be kept to a minimum. Some topologies do not use an input coupler, for example the *Transformer-Feedback* amplifier and the *RF-op-amp*, with these the NF should not change but the input and output impedances of these topologies will change more than with those amplifiers that use a directional coupler.

Finally, adding feedback increases the chance of the amplifier being unstable and this will need to be closely watched during the design. There are now two instability loops associated with the amplifier, the normal mechanism around the transistor itself and a second loop when the feedback path is added.

## 1.4.1 Simulation Results of an Ideal LF Amplifier

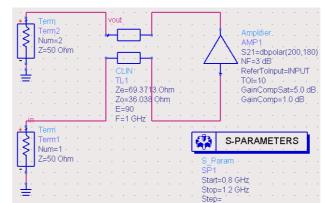

A good demonstration of the advantages of lossless-feedback is to simulate an ideal lossless-feedback amplifier shown in Figure 1.13. In this example a lossless coupled line (CLIN) is added to an ideal gain-block (AMP1) that has a variable gain and a NF of 3dB. The gain of the gain-block and the coupling level can be independently controlled.

Figure 1.13 – Simulation circuit for an Ideal Norton Amplifier

The RF coupler is set to 10dB with Zo = 36.04-Ohm and Ze = 69.37-Ohm; the calculation of Zo and Ze can be found in the MathCAD sheet "Values for Discrete Component Coupler" Appendix A (page 88). The gain-block is an inverting amplifier with its gain adjusted from 5 to 50dB. Unlike a real amplifier there is no variation of phase and gain with frequency.

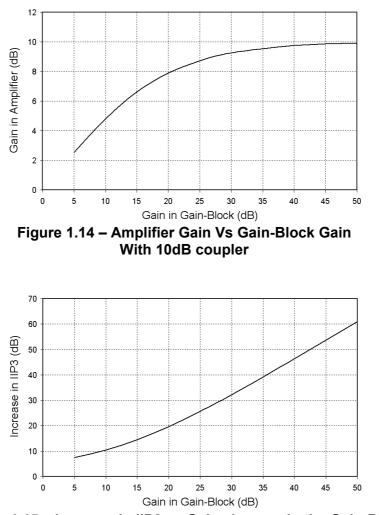

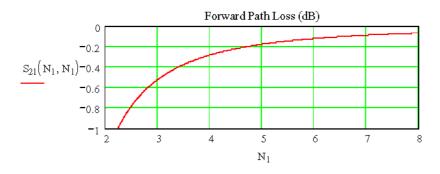

Figure 1.14 shows how the amplifier gain converges to the value of the coupler, in this case 10dB when the gain in the gain-block is set to a very high level. If the gain of the gain-block is 20dB (10dB above the coupling level), then the amplifier will give 7.9dB gain.

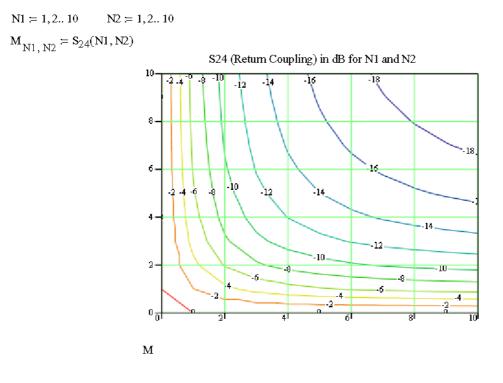

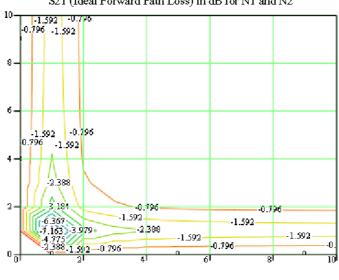

Figure 1.15 shows how the amplifier IIP3 increases as the gain the gain-block increases. If a gain of 50dB can be obtained from the gain-block, then the IIP3 of the amplifier would increase by 60dB, which is a remarkable result. It may be possible to achieve such a large gain using a multiple transistor stage amplifier. At more realistic gain of 20dB, the ideal amplifier shows an improvement of 20dB in the IIP3.

The advantage to the system designer of a high IIP3 can be realized in two ways. It either allows the design of a very robust front-end amplifier that requires little filtering before the mixer, or it allows the power consumption in the amplifier to be reduced considerably and yet still meet the IIP3 requirements imposed by the system design.

Figure 1.15 – Increase in IIP3 as Gain changes in the Gain-Block With 10dB Coupler

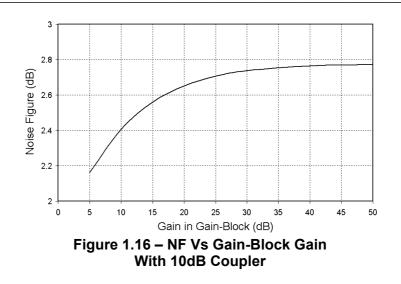

Figure 1.16 shows how the NF of the ideal system varies as the gain in the gain-block changes. Interestingly, the NF of the amplifier is found to be less than the NF of the gain-block. The reason for this is that a percentage of the input power reaches the output directly through the coupler and does not pass through the amplifier.

## 1.5 Project Goals

The aim of this project is to investigate and to build a lossless-feedback amplifier on an IC using the UMC-025um RF CMOS process that will demonstrate the principles of this group of amplifiers. The amplifier topology chosen for integration is the topology presented in the original *Norton Amplifier* patent [1] and shown in Figure 1.8. This is the simplest of the lossless feedback amplifiers; it uses a 50-Ohm RF directional coupler as the feedback path and a simple one-transistor amplifier as the gain-block. The coupler is designed and simulated separately to the gain-block. The gain-block is limited in the UMC process to CMOS transistors that are not ideal as gain-block requires 50-ohms input and output termination for optimum performance and the high input impedance of the CMOS transistors may be a challenge to this. However this is suitable choice to demonstrate the principles behind this group of amplifiers.

Chapter 2 describes the design of the Norton Amplifier; Chapters 3 explains layout choices with the final amplifier described in Chapter 4. The test results are presented in Chapter 5.

It is worth considering at this stage, the performance that has been achieved from other LNA designs using a CMOS process, and to use this information as a benchmark to write some design goals. Summaries of LNA performances have been presented in the literature [11] and shown here in Table 1.4. This shows that the typical performance of a CMOS amplifier is a NF=2.5dB, IIP3 = 0dBm, Gain 18dB, Operating voltage 3.3V and 10mW power consumption.

These summaries can be used to create some design goals for the Norton Amplifier design in Chapter 2 and these are listed in Table 1.5.

The input and output impedances are required to be 50-Ohm which is necessary if the amplifier is to be accurately measured and characterized using standard test equipment. The proposed gain is 8dB, which is a compromise as the gain of the amplifiers in table 1.4 are typically 20dB and this will be reduced considerably when feedback is added. The supply voltage is set to 1.25V, this is chosen because the simple Norton amplifier uses a single transistor stage and will thus operate comfortably at this low voltage. In addition this will help the amplifier meet the proposed the power consumption requirement.

|                    | Typical     | LNA performance in recent reported designs (2.4GHz or beyond) |          |         |         |         |         |

|--------------------|-------------|---------------------------------------------------------------|----------|---------|---------|---------|---------|

|                    | Values [12] | LNA in                                                        | LNA in   | [13]    | [5]     | [11]    | [11]    |

|                    |             | Fig. 1                                                        | Fig. 5   |         |         |         |         |

| NF                 | 2 dB        | 2.2 dB                                                        | 2.4 dB   | 2.5 dB  | 2.4 dB  | 2.5 dB  | 3 dB    |

| IIP <sub>3</sub>   | -10 dBm     | 1.3 dBm                                                       | -3.4 dBm | 2 dBm   |         | -10 dB  | -10 dB  |

| 1-dB Compression   | -20 ~ -25   | -18 dBm                                                       | -21 dBm  | -12 dBm |         |         |         |

|                    | dBm         |                                                               |          |         |         |         |         |

| Power Gain         | 15 dB       | 15 dB                                                         | 20 dB    | 19.9 dB | 19 dB   | 22 dB   | 18 dB   |

| Input Return Loss  | -15 dB      | -17 dB                                                        | -19 dB   |         | -10 dB  |         |         |

| Output Return Loss | -15 dB      | -23 dB                                                        | -21 dB   |         |         |         |         |

| Reverse Isolation  | 20 dB       | 24 dB                                                         | 35 dB    | 47.8 dB |         |         |         |

| Stability Factor   | > 1         | 1.4                                                           | 3.6      |         |         |         |         |

| Frequency          |             | 2.4 GHz                                                       | 2.4 GHz  | 2.4 GHz | 2.4 GHz | 2.5 GHz | 3 GHz   |

| Power Dissipation  |             | 4.8 mW                                                        | 7.2 mW   | 14.7 mW |         | 12 mW   | 12 mW   |

| Process            |             | 0.25 µm                                                       | 0.25 µm  | 0.35 µm | 0.5 µm  | 0.35 µm | 0.35 μm |

| Supply Voltage     |             | 3.3 V                                                         | 3.3 V    | 2 V     | 3 V     | 1.5 V   | 1.5 V   |

| Year               |             | 2001                                                          | 2001     | 2001    | 1999    | 1999    | 1999    |

Table 1.4 – Summary of CMOS LNA Performance [11]

| Linearity                       | IIP3 = +20dBm                                                                                                                        |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Gain                            | +8dB                                                                                                                                 |

| Bandwidth                       | 1.5 to 2GHz,                                                                                                                         |

| Input &<br>Output<br>Impedances | 50-Ohm with VSWR of 2:1                                                                                                              |

| Stability                       | Unconditionally Stable.                                                                                                              |

| Noise<br>Figure                 | 3.5dB max. Aim for a NF of less than 3dB, but not thought possible as the coupler is expected to add loss and degrade the NF by 1dB. |

| Voltage                         | 1.25V                                                                                                                                |

| Power                           | Power dissipation 15mW max.                                                                                                          |

Table 1.5 – Design Goals for Norton Amplifier

## 2 NORTON AMPLIFIER DESIGN

## 2.1 Overall Design Philosophy

This chapter explains the design of the simple Norton lossless-feedback amplifier. The topology of this amplifier is from a solution patented in 1971 [1] by D Norton of the Anzac Corporation and shown in Figure 1.7. In this solution two independent transformers are wound to form a single RF directional coupler [14] that has zero phase-shift between ports P4 and P2. Some of the output power from the transistor at P4 is fed back to its input port P2 at zero-phase, thus creating a feedback path in much the same way as a resistive element could be used.

With this topology, for optimum performance the base and collector impedance of the transistor should be the same as the impedance of the IN and OUT ports. For a 50-Ohm amplifier the base and collector impedances should be 50-Ohm.

The design of this amplifier divides into two parts; design of the RF directional coupler and design of the gain-block. Section 2.2 of this report investigates the properties of a number of RF directional couplers; section 2.3 investigates the different gain-blocks with the complete amplifier, combining the two parts in section 2.4.

Figure 2.1 – Norton Lossless Feedback Amplifier [6]

## 2.2 Design of RF Directional Coupler

The RF directional coupler feeds power back from the output of the amplifier to the input, thus forming the feedback path. Ideally the coupler has no loss in the two wanted signal paths, from P1 to P2 and P4 to P3, as this reduces the amplifier gain and adds noise. In addition, the phase-shift through the coupler needs to be well controlled and close to zero degrees as the power feeds back from P4 to P2.

Three coupler options are investigated for suitability, the branch-line coupler, the discrete component transmission line coupler and finally the transformer coupler.

## 2.2.1 Branchline Coupler

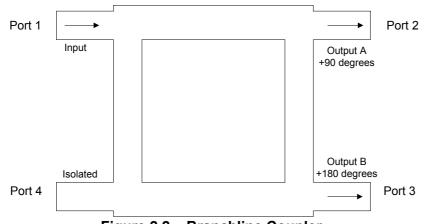

A *Branchline-coupler* is shown in Figure 2.2. This comprises of four transmission lines sections each with a length of 90-degrees and each of defined impedance. The coupler can be designed such that the output powers at Port A and Port B are unequal, with either most of the power outputting at Port A or most at Port B.

Two MathCAD sheets are written that calculate the line impedances for both of these options with different coupling levels. These are be found in Appendix A, pages 86, 87. These sheets start by calculating the required line impedances and then converting this to equivalent discrete components values.

Figure 2.2 – Branchline Coupler

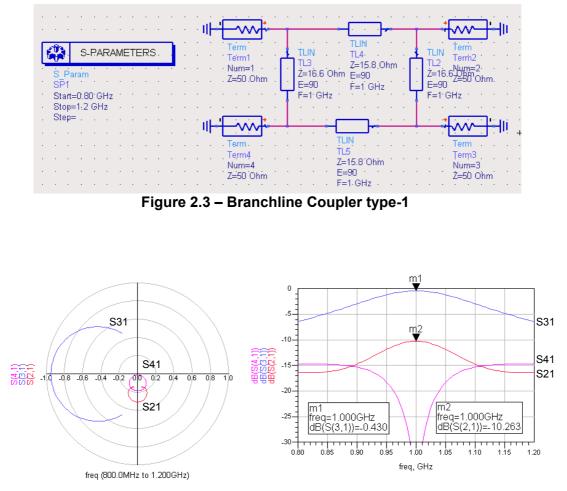

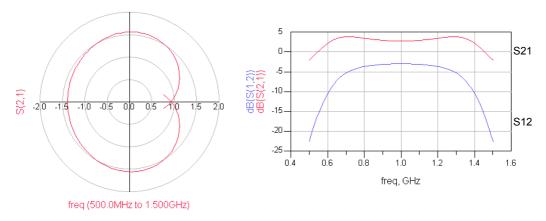

Using the MathCAD design sheet on page 86, an RF coupler can be designed with a coupling factor of 10dB, where most of the input power goes from port 1 to port 3, and has a 10dB coupling from port 1 to 2. Such a coupler is simulated using ADS and shown in Figure 2.3 with the results in Figure 2.4. The losses in the forward path are 0.43dB and the coupling power (S43) is close to -10dB at the operating frequency and with a well-defined phase rotation.

Figure 2.4 – Simulation Results for Branchline Coupler type-1. The forward loss is 0.43dB and the coupled power is –10.26dB and has a well-defined phase rotation.

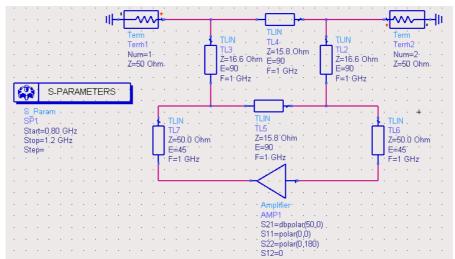

To use this coupler as part of an amplifier, an additional 90-degree phase rotation needs to be added in the feedback path and the gain-block itself needs to be non-inverting. Such an ideal amplifier is shown in Figure 2.5. The additional phase rotation is added using transmission lines components and these have the further advantage that they can be used to compensate for any unwanted phase shift in the amplifier.

Figure 2.5 – Amplifier Design using Branchline Coupler type-1

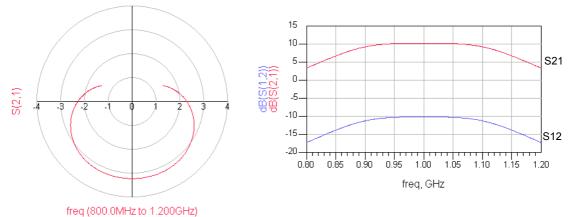

Figure 2.6 – Simulation Results for Branchline Coupler Amplifier type-1

The simulation results for this amplifier are shown in Figure 2.6 and show that an excellent gain and frequency response can be obtained. The gain-block in this simulation is set to 50dB with zero-degrees phase shift rather than a more realistic gain, as it better demonstrates the principles behind this configuration. The reverse isolation is as predicted, equal to the coupling value.

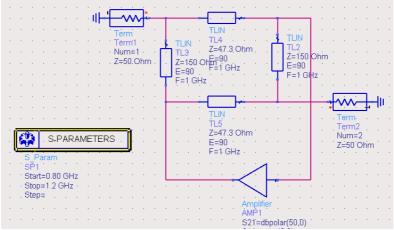

There are a number of alternate variations that may be used with the *Branchline-coupler* that will remove the requirement for this additional phase shifting circuit and will give the amplifier a greater bandwidth. Two alternate topologies are shown in Figures 2.7 and 2.9. The simplest change is to use the alternate coupler design (Figure 2.7) where most of the input power goes from port 1 to port 2 with the -10dB coupling from port 1 to 3. The advantage with this topology is that the feedback path around the amplifier already travels through two 90-degree sections and is therefore at the correct phase for stable feedback without additional circuitry with a non-inverting gain-block.

An amplifier using this coupler variant is shown in Figure 2.7, again with a 50dB gain-block and with the simulation results in 2.8. Surprisingly this amplifier has a wider bandwidth even though the feedback path is also through two 90-degree sections each with a frequency response. The gain and reverse isolation are also 10dB and -10dB, equal to the coupling value.

Figure 2.7 – Branchline Coupler Amplifier type-2

Figure 2.8 - Simulation Results for Branchline Coupler Amplifier type-2

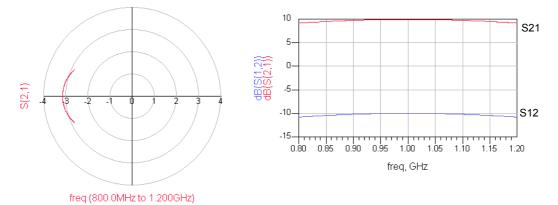

The final improvement is to consider the use of a multiple section Branchline coupler that will increase the bandwidth and also remove the requirement for additional phase shifting. A circuit showing a 3dB amplifier with a two section Branchline coupler is shown in Figure 2.9. The simulation results show a bandwidth of 0.5 to 1.5GHz, the amplifier shows excellent results.

Figure 2.9 - Branchline Coupler Amplifier type-3

Figure 2.10 - Simulation Results for Branchline Coupler Amplifier type-3

## 2.2.1.1 Branchline Coupler on the IC

The Branchline coupler seems to shows promise as a coupler that could be used in the design of a lossless-feedback amplifier, but before moving into a detailed design phase a more realistic coupler needs to be simulated with losses included. To estimate the expected losses, each of the 90-degree sections can be translated into a C-L-C transmission line. This is essential for integration, as a 90-degree transmission line is several centimeters long at 2GHz and is impractical on an IC.

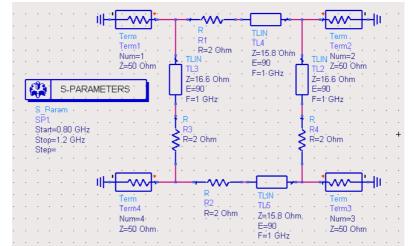

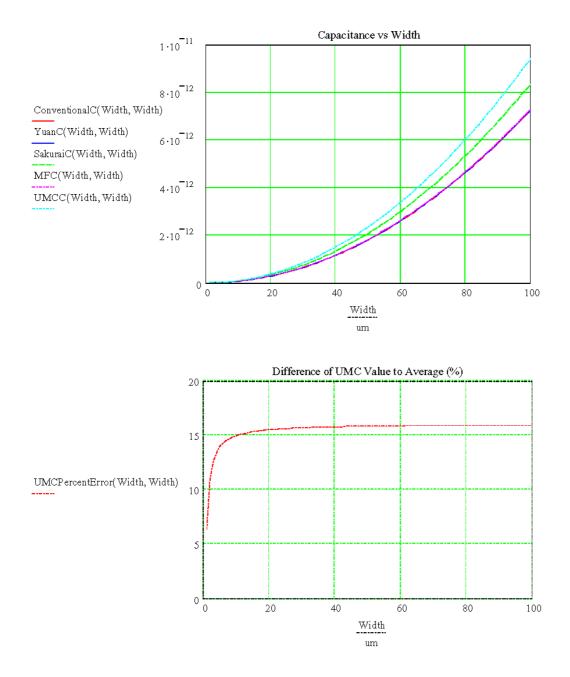

For the Branchline Coupler shown in Figure 2.3, at 2GHz for a –12dB coupling, the inductance values are 1nH and the capacitance is 12.5pF. The equivalent series resistance for this inductor is estimated by comparing the UMC model [15] for the standard 1nH square inductor. The Q of the UMC inductor is 4 at 1.8GHz, which corresponds to an equivalent series resistance of 2.8-Ohm. These simulations are made with a lower value than this at 2-Ohm as it is expected that using wider tracks will reduce the losses. The schematic with these series resistors is shown in Figure 2.11 and with the results in Figure 2.12.

The results shows a large deviation from the ideal coupler (Figure 2.4) that renders this topology unacceptable for integration on an IC and unlikely to give acceptable results when used as part of a lossless feedback amplifier. The losses in the transmission paths (S21 & S34) are 3.3dB and the coupling level has dropped by over 4dB to -14.3dB.

Figure 2.11 - Branchline Coupler type-1 with Series Resistance

Figure 2.12 – Simulation Results for Branchline Coupler type-1 with Series Resistance

Some consideration was given to using the alternative coupler configuration shown in Figure 2.7, but with a line impedance of 150-Ohm required in this design which correspond to an inductance of 15nH, this would be difficult to achieve and will result in a large coupler.

## 2.2.2 Transmission Line Coupler

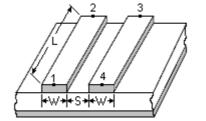

The second option for an RF directional coupler and perhaps the most obvious starting point, is the simple transmission line coupler shown as in Figure 2.13 and this was used in the simulations to demonstrate the principles behind this group of amplifiers in Section 1.4.1.

Figure 2.13 – Microstrip Coupled Line

A 10dB coupler is obtained with Zo = 36.04-Ohm and Ze = 69.37-Ohm. Using the line impedance calculator *LineCalc* in *HP ADS* and with the dimensions for H, T and Er from the UMC process [16], this corresponds to a line length of 22mm at 2GHz. This length is clearly unacceptable for integration on an IC, although Ozazaki [21] has produced a coupler of this type with an overall area of 0.9mm by 0.12mm and operates from 10 to 17GHz by meandering the Microstrip tracks on a GaAs substrate.

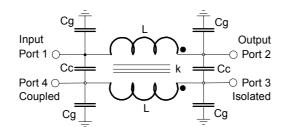

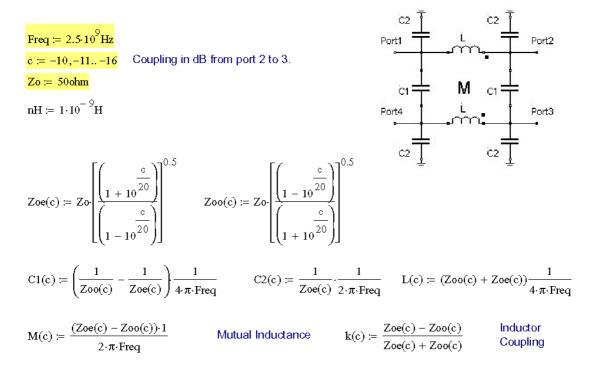

To achieve the size constraint it is necessary is to build the coupler using discrete components. The design equations for this are shown in the MathCAD sheet on page 88, with the formulas taken from an IEEE MTT paper by Hogerheiden J [17], and shown diagrammatically in Figure 2.15.

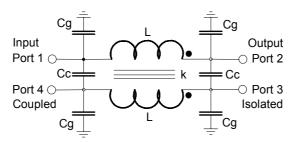

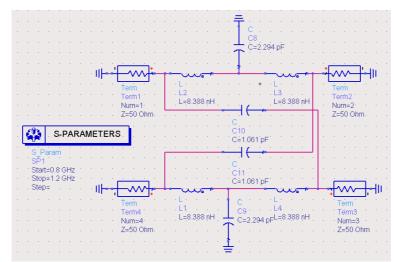

Figure 2.15 – Discrete Component Coupler

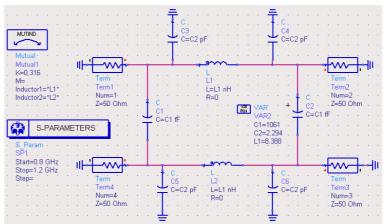

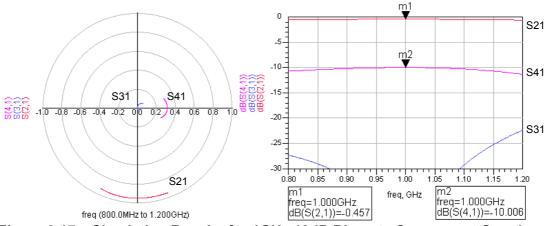

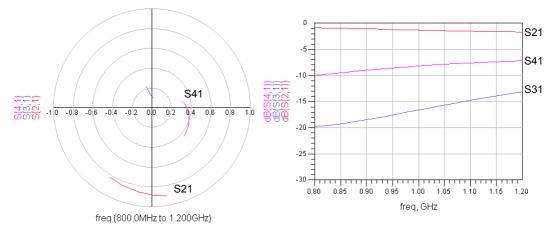

A suitable 10dB coupler at 1GHz is shown in Figures 2.16, and the results for the ideal lossless coupler are presented in Figure 2.17. It can be seen that the gain and phase response of S41 is excellent, giving very close to 10dB coupling at the center of the band and with a wider bandwidth than that obtained from the *Branchline-coupler*. Other aspects of the coupler are also good, the forward path loss is 0.47dB and the coupler shows greater than 25dB of isolation (S31) over a wide bandwidth.

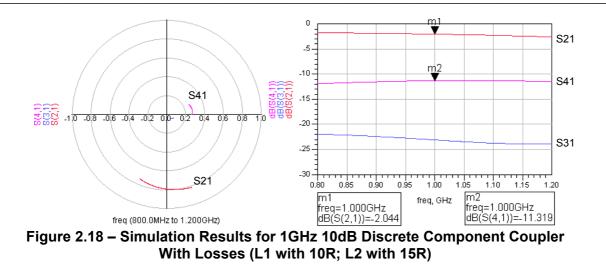

Before moving further into the design it is worth taking time to run a simulation with practical losses that will be experienced if this design is integrated on an IC. The equivalent series resistance is estimated from UMC model [15] for an 8nH square inductor, where the Q of this inductor is given as 6 at 1.8GHz. This corresponds to a series resistance of 15-Ohms, but as before it is expected that a practical implementation with wider tracks will produce lower series resistance of 10-Ohms for L2 and 15-Ohms for L1. The difference in the resistance for L1 compared to L2 is because one of the inductor tracks will be on the metal-5 layer that is 2µm thick and the other inductor will be on metal-4 that is 0.6µm thick.

The simulation results are shown in Figure 2.18. This lossy coupler is still reasonable with good phase rotation in the S41 path. The S41 coupling is 11dB and the forward path loss is 2dB.

Figure 2.16 – 1GHz 10dB Discrete Component Coupler

Figure 2.17 – Simulation Results for 1GHz 10dB Discrete Component Coupler Without losses

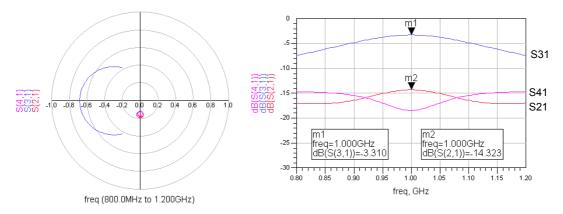

A disadvantage of this topology is that the coupler needs to be designed with a small amount of mutual coupling between the turns that may be hard to achieve and it is worth investigating an alternative coupler configuration shown in Figure 2.19 [22] that uses four inductors but does not require mutual coupling between them.

Simulations have shown that this circuit works well with less than –15dB of coupling, but at higher coupling levels the phase rotation and coupling levels are not well defined. Results for the coupler at 1GHz and at 10dB and 20dB coupling are shown in Figures 2.20 and 2.21. These show a poor performance at 10dB but good performance at 20dB.

Apart from the poor phase response at higher coupling levels, the circuit has twice the number of inductors which will consume approximately four times the IC area of the coupled inductor version. In addition the circuit has approximately twice the path loss compared to the coupled version.

Figure 2.19 – 1GHz 10dB Discrete Component Coupler type 2

Figure 2.20 – Simulation Results for 10dB Discrete Component Coupler type 2

Figure 2.21 – Simulation Results for 20dB Discrete Component Coupler type 2

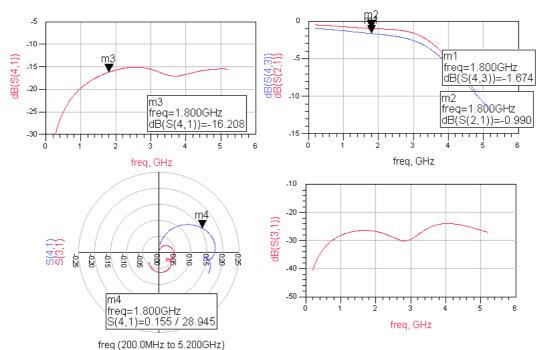

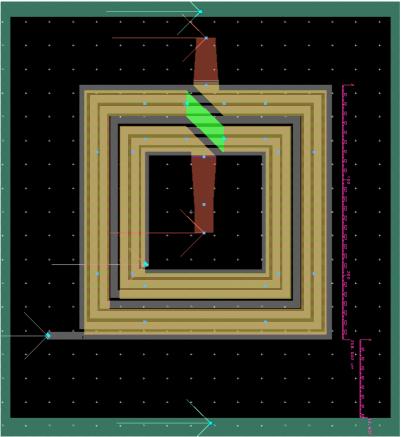

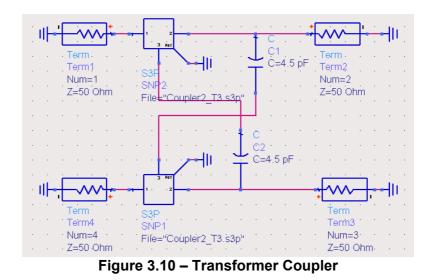

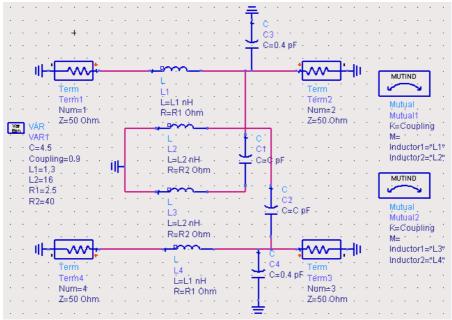

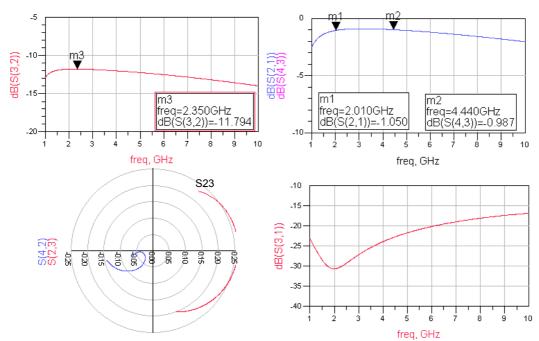

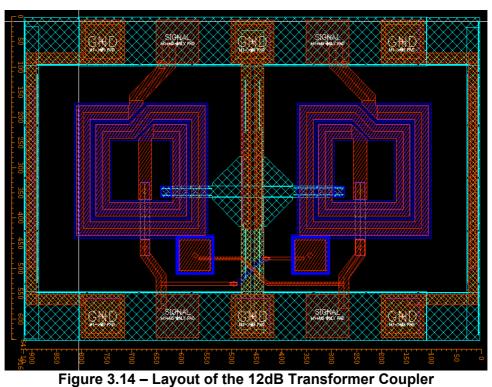

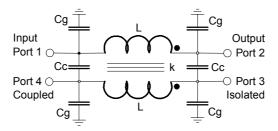

## 2.2.3 Transformer Coupler

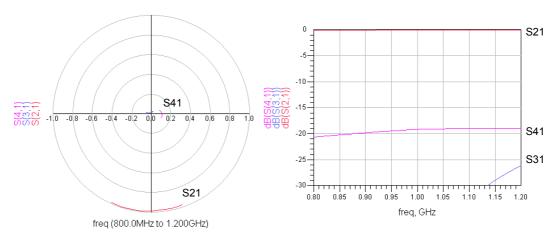

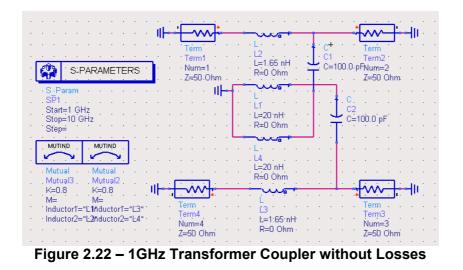

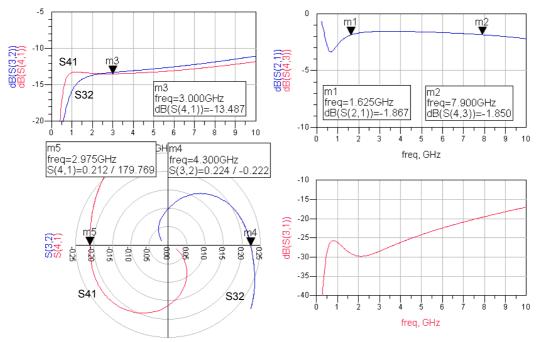

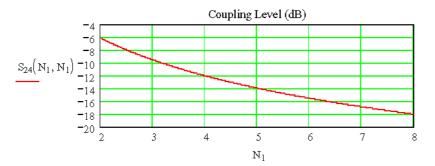

The third coupler option investigated is the transformer coupler as used in the original *Norton Amplifier* patent, with the design equations described in a paper by Kajfez [14]. These equations are presented using the MathCAD sheet on page 93 and show that a turns ration of 3.5:1 is a suitable starting point for the design that will give approximately 11dB of coupling under ideal conditions.

No reference can be found of a coupler of this type having been built on an IC before and this paper implies that a tight coupling (k) of better than 0.99 is required to get good performance at these frequencies. Normally the best coupling (k) that can be achieved using the planar spiral transformers is 0.9 [28] with k = 0.8 considered more likely.

To test this, a simulation circuit is constructed shown in Figure 2.22 that has a value of k = 0.8 and with a primary inductance value of 1.65nH; both of which are considered achievable. The inductance value is proportional to the square of the number of turns, so with a turns-ratio of 3.5 and with 1.65nH primary inductance, the inductance value of the secondary turns is estimated to be 20.21nH with 20nH used in the simulation.

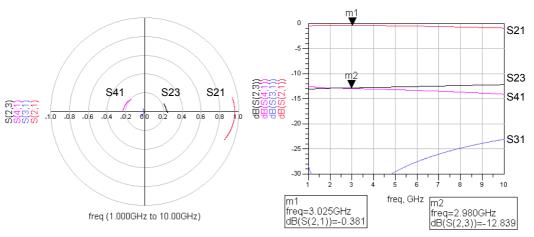

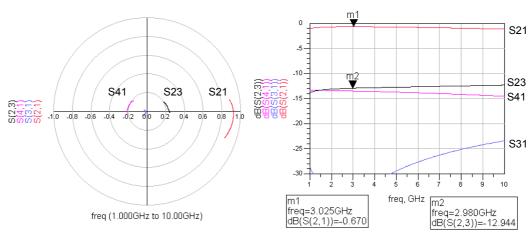

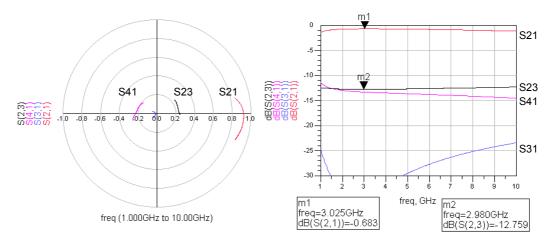

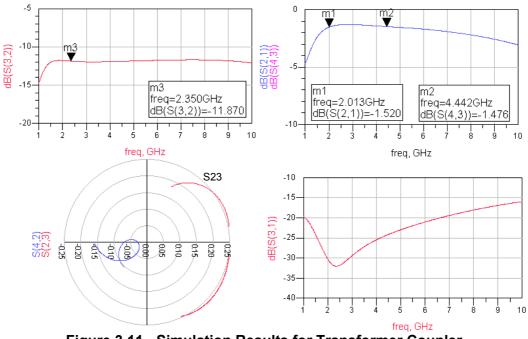

The results are shown in Figure 2.23 and it is important to notice that these results are presented over a much wider bandwidth than with the previous coupler designs. The forward path loss (S21) is 0.38dB at 3GHz, and there is a small variation of this up to 10GHz. The coupling (S23) is reasonably flat and has a stable close-to-zero phase shift over this band. The isolation (S31) is excellent.

Interestingly, it can be seen that the coupler is not symmetrical and if reversed such that S41 is the feedback path, it can be seen that there will be a 180-degree phase shift, which will allow a non-inverting amplifier to be used as the gain stage.

Figure 2.23 – Simulation Results for Transformer Coupler without losses

To check the suitability of this coupler for integration on an IC we need to carry out further simulations with resistive losses; a 2-Ohm series resistance is added to1.6nH inductors and 20-Ohms to the 20nH inductors. The simulation results shown in Figure 2.24 indicate that this circuit is a robust solution with the forward path loss increasing by 0.3dB. Perhaps the only concern is the coupling (S23) that now has a slope over the frequency band.

A simple solution was found to flatten the coupling level over this bandwidth by reducing the decoupling capacitors C1 and C2 from 100pF to something smaller. This of course is advantageous in integrating this design on an IC as the smaller capacitors take up less space. The circuit is simulated with the capacitors set to 6pF and the results shown in Figure 2.25.

Figure 2.24 – Simulation Results for Transformer Coupler with Losses

Figure 2.25 – Transformer Coupler with 6pF Decoupling Capacitors

## 2.2.4 Conclusion on Coupler Options

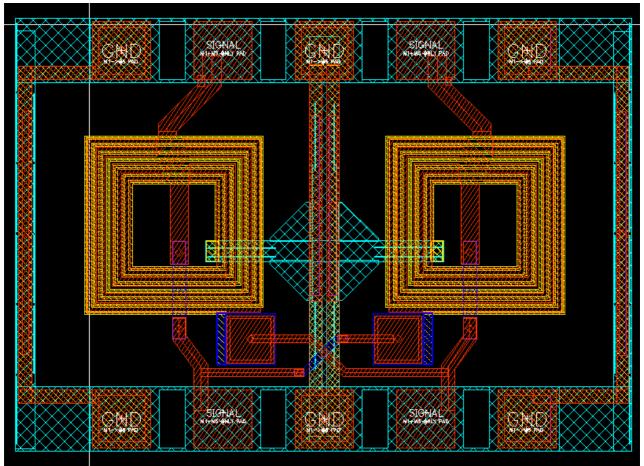

Three types of coupler have been investigated in this section. The *branch-line* coupler was found to be too sensitive to the expected losses associated with integration and for this reason cannot be used as part of the lossless feedback amplifier. The discrete component transmission line coupler shows several advantages, it is small, requiring two overlapping inductors and with an easily achievable coupling coefficient. The disadvantage is that it is not symmetrical with the construction requiring two different metal layers, each with different conductivity. Nevertheless its small size and good bandwidth gives it advantages. The third coupler investigated is the transformer coupler. This has the widest bandwidth of the couplers investigated, but runs the risk that the high coupling level required is unachievable.

The coupler chosen for integration with the gain-block to form part of the Norton Amplifier is the discrete component coupler. The input path will be on the top metal layer with the highest conductivity to minimize the input loss and the affect on the Noise Figure. Both the discrete component coupler and the transformer coupler are built and tested individually and the results presented in Section 5.

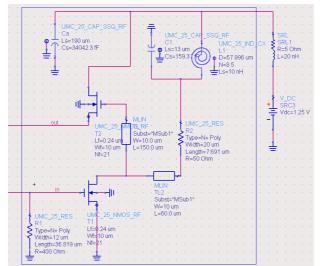

## 2.3 Design of Gain-Block

## 2.3.1 Single FET Gain-Block

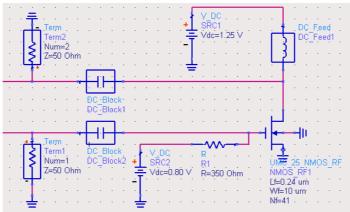

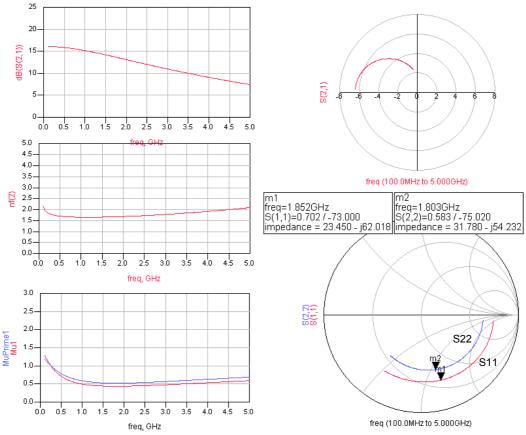

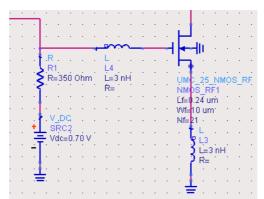

The simplest gain block that can be built is with a single FET stage, and it is this topology but with a bipolar transistor that was presented in the original Norton amplifier patent. A simulation of the simple FET stage is set up in Figure 2.26 and the results shown in Figure 2.27. The amplifier is not matched, as we will see later that the matching circuits will result in an unwanted phase delay.

The circuit takes 15mA and has a forward path gain of 13dB at 2GHz. This is too low to be useful with 20dB gain considered the minimum for the circuit to be useful, the Noise Figure however is good at 1.8dB, but the stability measures show that this amplifier is likely to be unstable. From this simple construction we can see that a simple transistor amplifier will not work, it does not have sufficient gain and has a tendency to be unstable and consequently it is necessary to consider a multiple transistor amplifier solution.

Figure 2.26 – Single FET Amplifier Gain Block. Gate length 0.24µm and Gate width 41 x 10µm.

Figure 2.27 – Performance of Single FET Amplifier Gain Block

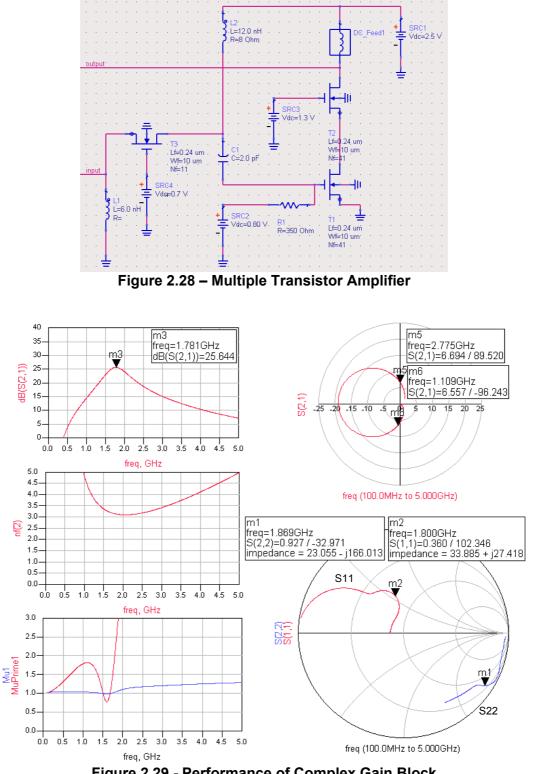

## 2.3.2 Multiple Transistor Gain-Block

The logical step from a single FET amplifier is to consider a multiple transistor amplifier such as the amplifier shown in Figure 2.28. In this design a common-gate input configuration was chosen to present a good 50-Ohm input match over a wide bandwidth and this was followed by a cascode FET configuration for high gain. The results of this amplifier are shown in Figure 2.29, the gain has increased to a satisfactory 27dB at 1.8GHz; the NF is worse at 3dB; the stability has improved greatly and the input impedance is closer to 50-Ohms, as expected.

Figure 2.29 - Performance of Complex Gain Block

Generally this amplifier looks like a reasonable candidate for integration as part of an LFA and to test this, the amplifier is added to a 10dB transformer-type coupler of the topology shown in Figure 2.22. The results of the complete amplifier are shown in Figure 2.30 and this is the first time in this report that a realistic lossless feedback amplifier is constructed and analyzed.

There are a number of interesting observations that can be made about this LFA. Firstly, the forward gain (S21) is close to the 10dB expected and is flat across a wide bandwidth. Secondly, the input and output impedance are both closer to 50-Ohms and of an impedance that is better than the gain block. It is interesting that with this type of amplifier both the input and output impedances tend to improve.

Figure 2.30 - Performance of LFB Amplifier with Complex Gain Block from Figure 2.28 combined with wide bandwidth RF directional Coupler from Figure 2.22

The worst performance change is the stability index as calculated by  $\mu$  and  $\mu'$  which now go well below 1, the value required for unconditional stability. At some frequencies *both* stability indices are less than 0, which indicates that the amplifier will be unstable when connected to 50-ohm. The reason for this worsening of stability can be explained by examining the S21 polar plot of the basic amplifier, shown in Figure 2.29.

Normally the output of the amplifier is inverting as seen by the polar plot cutting the x-axis on the left. Unfortunately, the phase of the amplifier output signal becomes positive at below 1.1GHz and above 2.8GHz and this is shown in Figure 2.29 with markers where the response cuts the y-axis. It is important to note that using a gain-block that gives gain with a positive phase is likely to cause the amplifier to be unstable.

The conclusion from this, is that a multi-stage amplifier circuit is unlikely to be usable as it is likely that the phase of S21 changes too much with frequency and will have gain with a non-inverting phase at some point in the frequency response. It is essential that the gain block is as simple as possible.

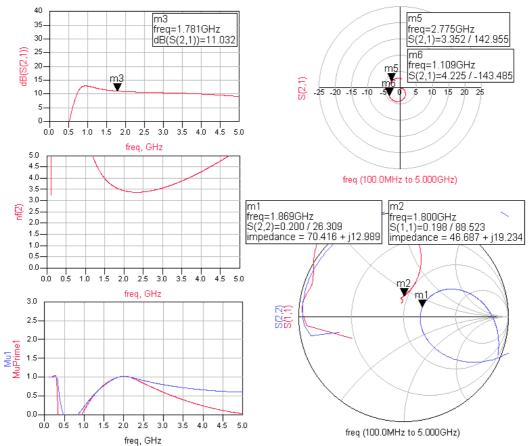

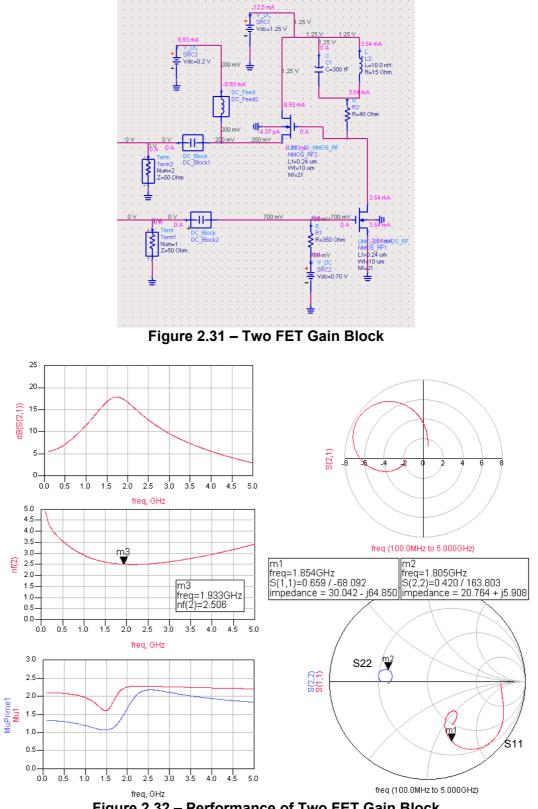

## 2.3.3 Two FET Gain-Block

The solution proposed is a two FET gain-block that uses a common source input FET to provide gain, followed by a second FET as a source-follower to improve the output current drive and lower the output impedance closer to 50-Ohm. The circuit is shown in Figure 2.31. The source-follower also provides gain with the advantage that it has little effect on the phase delay. It also provides reverse isolation, which should allow easier integration of the amplifier with the coupler.

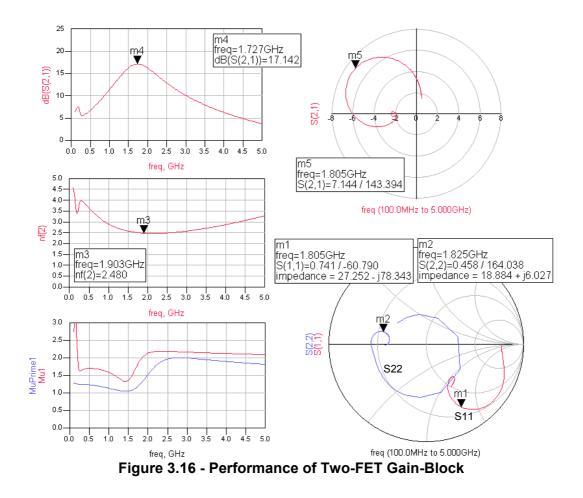

Figure 2.32 – Performance of Two FET Gain Block

The results for this gain-block can be seen in Figure 2.32. The forward gain peaks at 18dB, the NF has a minimum of 2.5dB and it is unconditionally stable. The S21 phase rotation is acceptable, with approximately 20° of phase error and the output impedance is 17-ohms and close to the real axis. These are reasonable results.

It is also worth pointing out that this amplifier is designed for 1.25V operation, as there is little advantage to operating the amplifier at a higher supply voltage. The simple amplifier construction makes it easy to operate at such a low voltage and this minimizes the power consumption.

## 2.3.4 Addition of Noise Optimization Inductor

The two-FET gain-block shown in the previous section is a reasonable solution that can be combined with a coupler to build a lossless-feedback amplifier. The major concern is the noise figure, which at 3dB is on the high side and will become higher when the coupler losses are included.

One option to reduce the noise figure is to consider adding a tuned circuit in series with the gatesource capacitance and in so doing increasing the Vgs voltage swing, and thereby reducing the noise figure and increasing the gain of the amplifier. The technique for doing this is outlined in this paper [18] and involves measuring the gate-source input capacitance and tuning this out with series inductors. The Cgs of the transistor is measured using the simulator, under the required operating conditions to be 1.28pF. For a tuned circuit to be included then the following equation can be used to calculate the series inductance.

$$Ls + Lg = \frac{1}{\left(2 \cdot \pi \cdot Frequency\right)^2 C_{gs}}$$

This gives a total inductance value of 6nH at 1.8GHz; this is divided into two with half placed in series with the *source* and half in series with the *gate* with the ratio of inductors to obtain a 50-Ohm input match. The final circuit is shown in Figure 2.33. An additional advantage of these inductors is the input impedance becomes closer to 50-Ohm and more real.

Figure 2.33 – Two FET Gain-Block with Cgs Tuning Inductors

The results presented in Figure 2.34 show an improved Noise Figure to 2.2dB and an improved input match (S11) closer to 50-Ohm. The concern with this modification is the polar response of S21 has rotated clockwise and with now a substantial part of the frequency response with a positive phase shift. This phase shift will cause this circuit to be unstable when combined with an RF directional coupler.

This reinforces the previous lesson that the amplifier must be of minimum complexity to reduce the phase shift in the S21 forward gain to ensure the lossless feedback amplifier remains stable.

Figure 2.34 – Performance of Two FET Gain-Block with Cgs Tuning Inductors

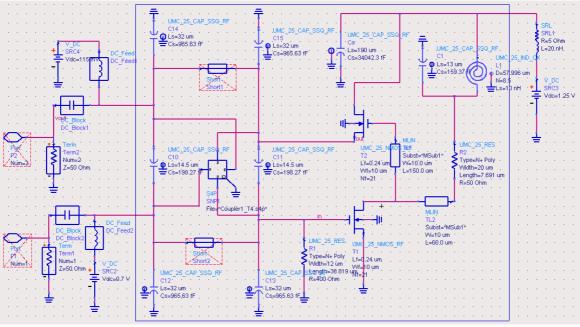

### 2.4 Complete Amplifier Design

The circuit components chosen to build a lossless-feedback amplifier are the transmission line, discrete component coupler shown in Figure 2.16 and the two-FET gain-block as shown in Figure 2.31. This coupler is the smallest of the couplers investigated and has a reasonably low loss in the input transmission path, as well as an acceptable although greater loss in the output transmission path. The path with the lower loss path is selected as the input path in order to minimize the affect on the amplifier noise figure. The coupler requires a small amount of coupling between the windings to function correctly, but this is not considered impractical.

The starting circuit for the design of the amplifier is shown in Figure 2.31. The forward gain peaks at 18dB at 1.8GHz and the NF has a minimum of 3dB, this is high although acceptable and the amplifier is unconditionally stable. The phase rotation of the forward transmission path (S21) is not perfectly inverting and has approximately 30-degrees of unwanted phase rotation at 1.8GHz and this will need to compensated in the design of the coupler for best stability.

The method to compensate for the amplifier unwanted phase rotation is to design the RFdirectional coupler to work above the required operating frequency. In doing so, this will result in a leading phase response from the coupler at the frequency of interest. Simulations have shown that a coupler designed at 2.5GHz will achieve the necessary phase rotation without a large variation in the coupled power at the frequency of interest, which may result in an unacceptable amplifier frequency response.

#### 2.4.1 Frequency Choice

The operating frequency is an important design consideration. It is limited at the low frequency end by the performance of the RF directional coupler. Operating below 1.5GHz will make this circuit large and have high forward path loss. Operation at the high frequency end is limited by the gain that can be obtained from the transistor stages, where it is necessary to obtain a minimum of 17dB of gain with the minimum of transistors. The optimum frequency is between 1.5 to 2GHz.

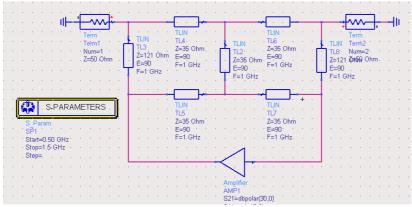

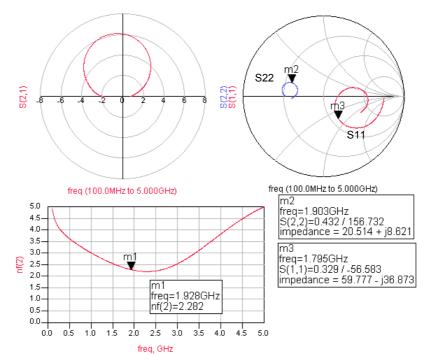

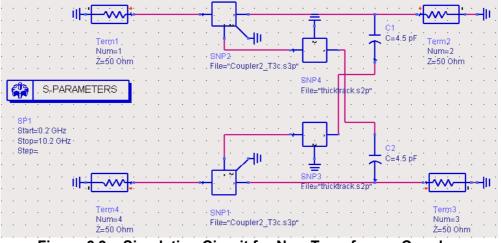

#### 2.4.2 Discrete Component Coupler at 2.5GHz

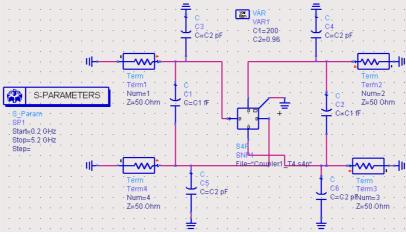

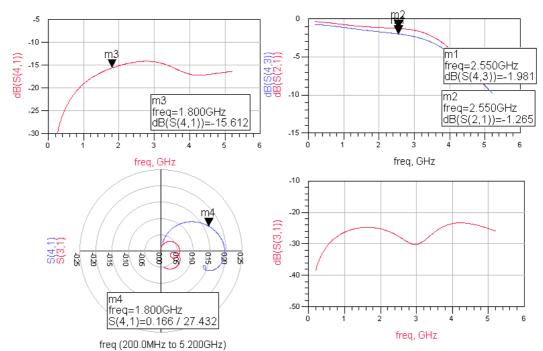

The required coupling power for the amplifier is 14dB at 2.5GHz; the circuit is shown in Figure 2.35 and the results in Figure 2.36.

Figure 2.35 – 14dB 2.5GHz Discrete Component Coupler

Figure 2.36 – Simulation Results for 14dB 2.5GHz Discrete Component Coupler

The coupling level is found by simulating the coupler as part of the amplifier and it depends on the overall gain required by the amplifier and the gain provided by the gain-block. The forward path transmission loss (S21) of this coupler is 1dB at 1.8GHz, and the amplifier output path loss (S43) is simulated to be 1.67dB. These losses are estimated by adding appropriate resistance in series with each transformer windings to simulate the expected inductor Q of the IC process. The forward transmission path is on the metal-5 layer of the IC, which is 2um thick and the return winding on the metal-4 layer and 0.6um thick. Further details of the IC construction can be found in section 3.1.

Simulations show the coupling level (S41), which is important for the amplifier stability and gain flatness to have a leading phase shift of about 29 degrees at 1.8GHz. The variation in coupling power has is approximately 1.5dB from 1.5 to 2GHz, although it is difficult to estimate how this will affect the gain of the complete amplifier.

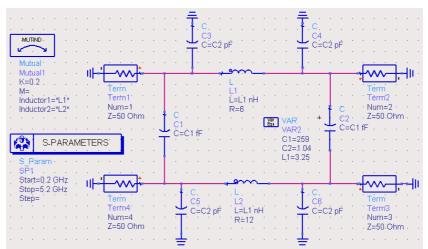

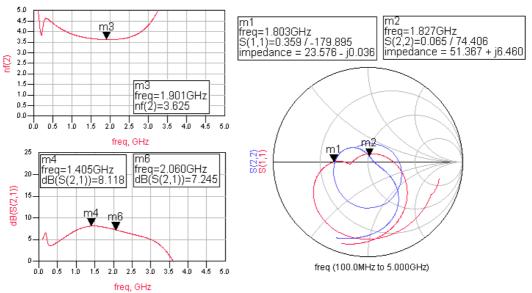

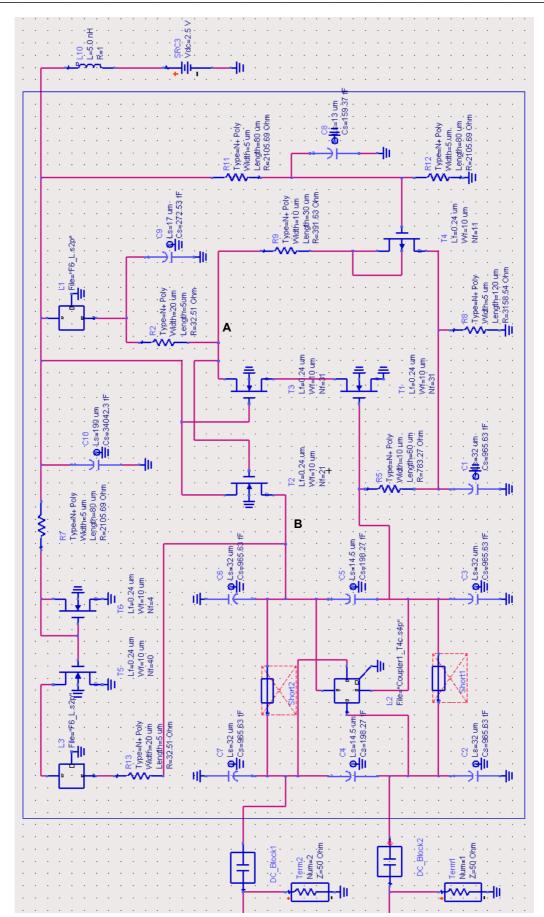

### 2.4.3 Complete Lossless Feedback Amplifier

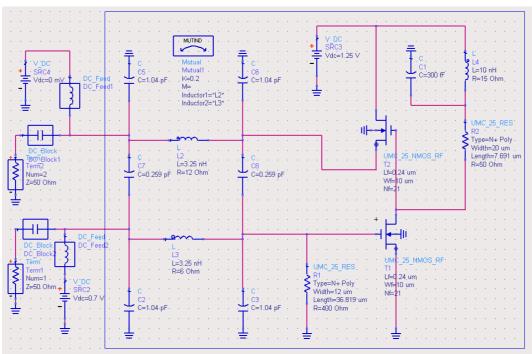

The gain-block and coupler are assembled together to build the complete amplifier in Figure 2.37 with the results presented in Figure 2.38. The Noise figure for the complete amplifier is simulated to be 3.5dB, which corresponds to adding the NF of the gain block at 2.5dB, plus an extra 1dB of loss in the forward path of the coupler. The Gain over the frequency range from 1.5GHz to 2GHz varies from 8.6dB to 7.5dB, this has more variation than is desired, but is not a bad starting point. The input and output impedance are very good considering the input and output impedance of the gain-block without the coupler shown in Figure 2.32.

Figure 2.37 – Lossless Feedback Amplifier

Figure 2.38 – Performance of Lossless Feedback Amplifier

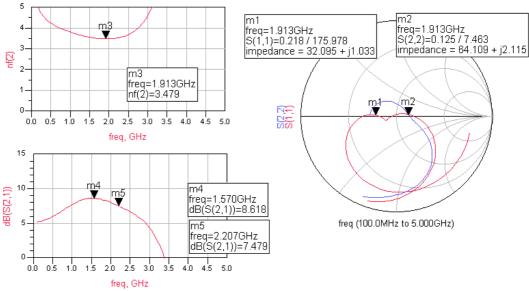

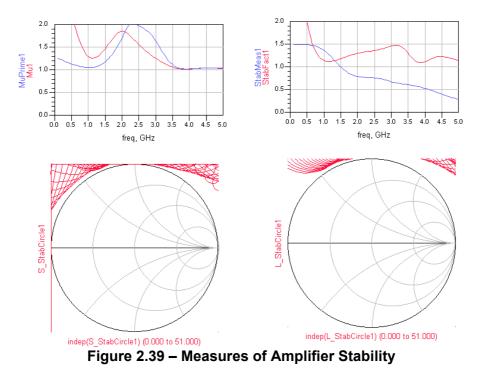

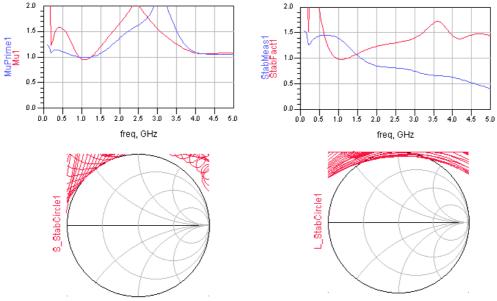

Of particular concern is the stability of this amplifier and these simulations show the amplifier to be unconditionally stable from 0 to 5GHz. All the different metrics for stability are shown here in Figure 2.39 including  $\mu$  and  $\mu'$ , as well as the conventional Rollet's calculation of stability and finally the input and output stability circles. All indicate unconditional stability.

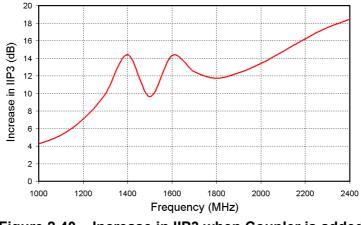

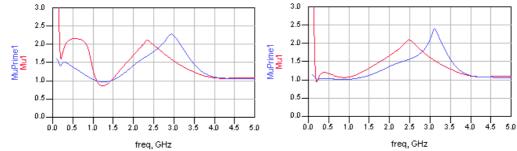

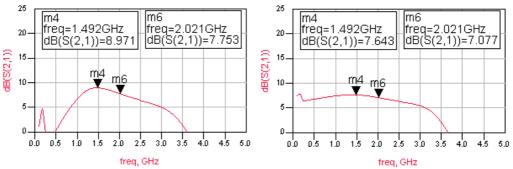

Adding the feedback around the amplifier is expected to improve the amplifier linearity and increase the IIP3. A simulation is set to measure the IIP3 across the band, both with and without the coupler. The improvement in IIP3 is shown in Figure 2.40 and shows a minimum of 10dB improvement can be expected from 1.2 to 2.4GHz.

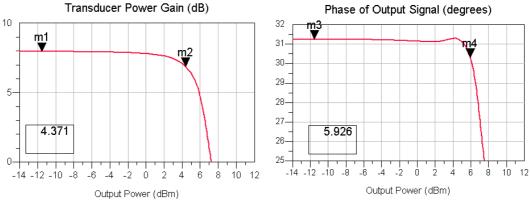

Figure 2.40 – Increase in IIP3 when Coupler is added

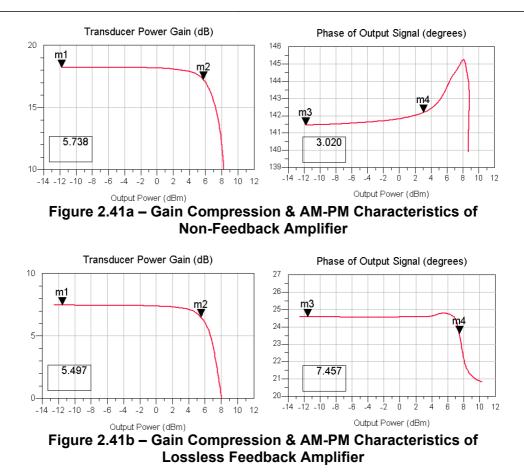

There are two other measures of linearity that need to be considered in the design; these are the 1dB compression point and the phase-power response, both of which are shown in Figure 2.41. The 1dB compression point of the amplifier is found to be worse by just over 0.2dB from 5.7dBm to 5.5dBm when the coupler is added. This actually indicates that the 1dB compression point out of the gain-block has improved by a small amount, as the output path loss in the coupler at 1.67dBm needs to be considered. If we are able to find a coupler without loss, then we would see a small improvement in this 1dB-compression point as predicted.

The phase response of the amplifier has also improved with the 1° phase error point increasing from 3dBm to 7.5dBm, and this is now higher than the output 1dB compression point.

# **3 DESIGN OF THE INTEGRATED CIRCUIT**

### 3.1 IC Construction

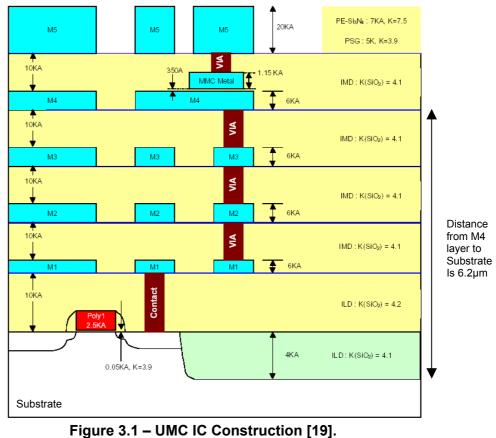

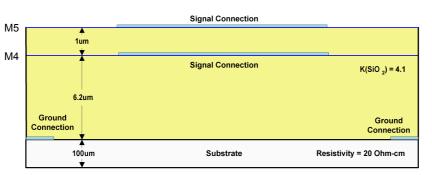

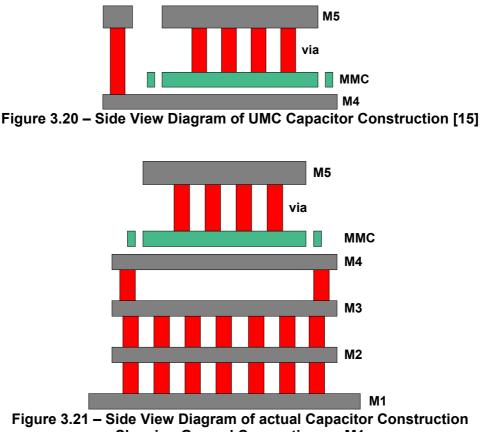

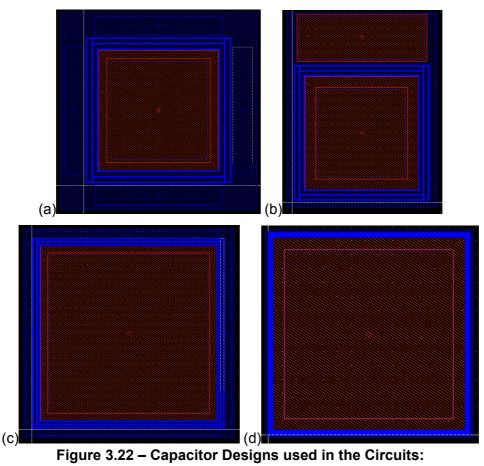

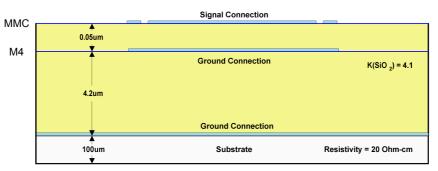

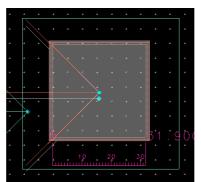

The starting point for the design of integrated circuit is to understand the IC construction. A figure that shows this for the process used in this project is given in a document by UMC [19] and duplicated here in Figure 3.1. The resistivity and dimensions are supplied in another document [16]. The top metal M5 is 2µm thick and has a resistance from 0.01 to 0.03-Ohm/sq; with 0.02-Ohm/sq used in the simulations. The other metal layers are 0.6µm thick and have a resistance from 0.035 to 0.075-Ohm/sq; with 0.053-Ohm/sq used in the simulations.

There is approximately 1um of  $SiO_2$  between each of the metal layers, and between 7.4 and 8.1µm from the bottom of the M5-metal layer to the substrate, with the substrate slightly doped to have an average resistivity of 20-Ohm-cm. The substrate losses are important in the design of the inductors, as the induced losses into the substrate account for approximately half of the effective series resistance of a inductor, the other half being attributed to the resistive losses from the metal.

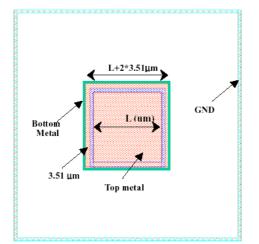

gure 3.1 – UMC IC Construction [19] The layers M are metal layers

An ambiguity was noticed between the UMC reference documents that define the spacing between the MMC metal layer and M4. Figure 3.1 shows this gap to be  $350A (0.035\mu m)$  whereas the second reference document [16] specifies that this gap to be between 450A to 550A (0.045 $\mu$ m to 0.055 $\mu$ m). This discrepancy becomes important when the capacitor values are calculated in section 3.3.1, when the value of 500A (0.05 $\mu$ m) is used.

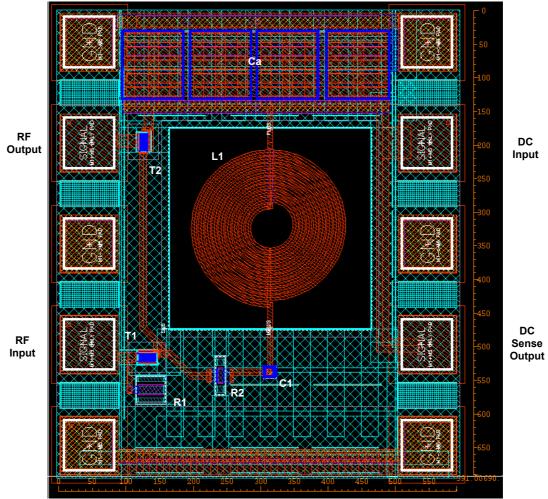

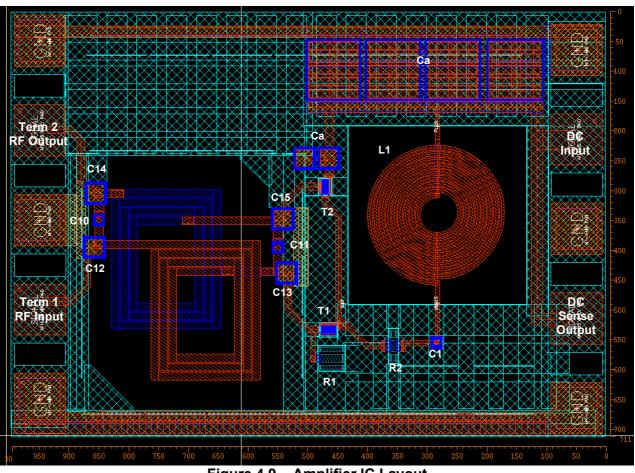

Section 3.2 describes the construction of three subassemblies, both RF directional couplers and the gain block. Section 3.3 describes the construction of the passive components.

## 3.2 Sub Assemblies

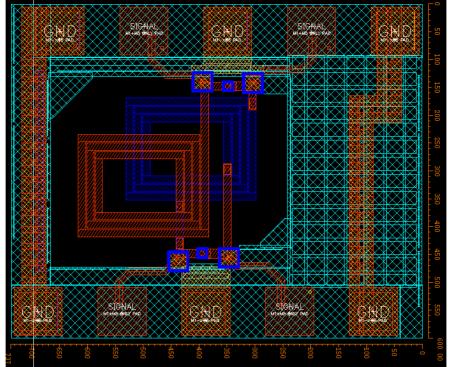

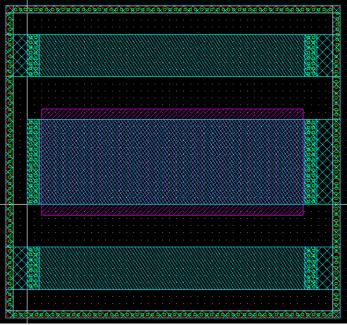

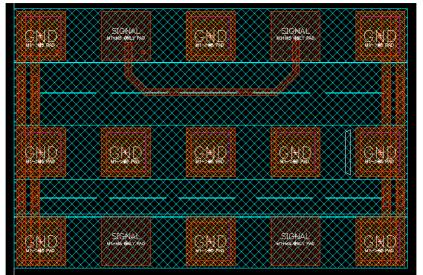

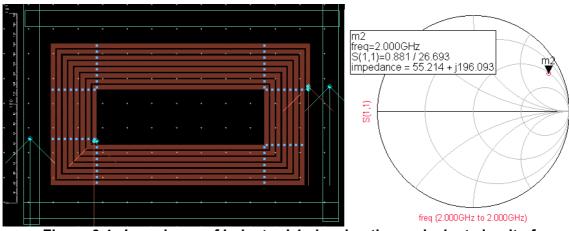

#### 3.2.1 Discrete Component Coupler

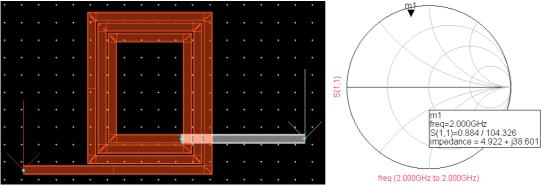

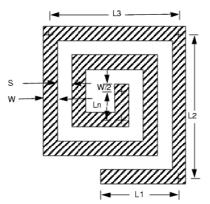

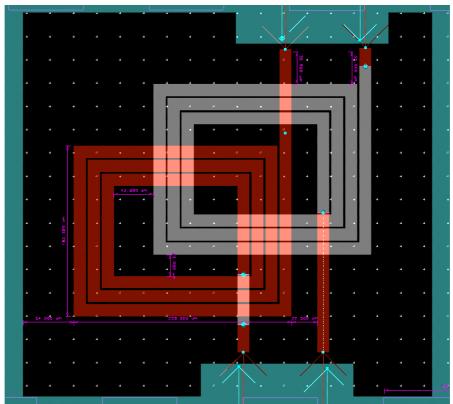

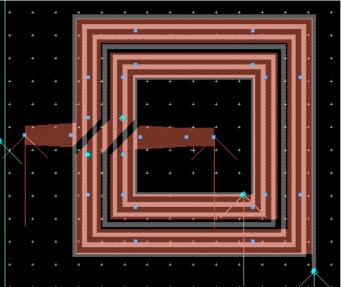

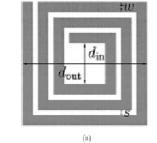

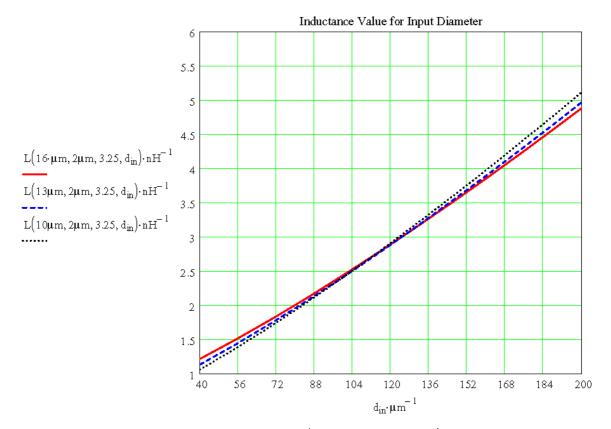

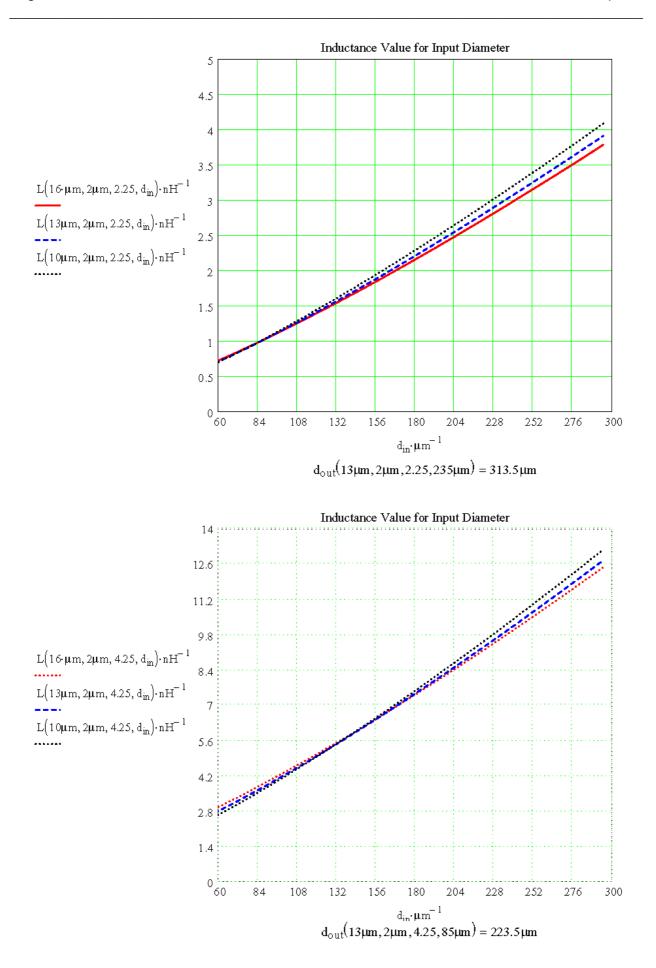

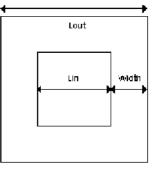

The discrete component coupler is designed in a number of sages; firstly the inductance of the top layer is calculated and simulated using the Momentum simulator [13]. An inductance value of 3.2nH is required for the design and as a starting point the inner diameter of a square inductor is estimated using the MathCAD sheet on page 91, which suggests an inner diameter of 125µm, an outer diameter of 233µm and with 3.25 turns of 13µm line-width and 2µm spacing. The starting estimate can be verified using a web page from the Stanford University site, which can be found at <a href="http://smirc.stanford.edu/spiralcalc.html">http://smirc.stanford.edu/spiralcalc.html</a>.

This inductor is then optimized using Momentum to get the dimensions shown in Figure 3.2. The momentum calculations are made without a guard ring that would normally circle the inductor in IC construction, with the second port shown on the right in this diagram as the ground return. In addition, even though this inductor is on metal-5 which is  $2\mu m$  thick, this thickness is not constructed as part of the simulation with the metal layers simulated as thin tracks.

The inductor shape was based on the ADS circuit component 'MRINDNBR' shown in Figure 3.3. The final dimensions were Ns=13, L1=270 $\mu$ m, L2=230 $\mu$ m, L3=170 $\mu$ m, W=13 $\mu$ m and S=2 $\mu$ m, and this inductor simulates to be 3nH with a series resistance of 4.9-Ohms, or a corresponding Q of 7.75 at 2GHz.

Figure 3.2 – Momentum Design of Inductor In this simulation the right-hand port is earthed

Figure 3.3 – (MRINDNBR) Inductor Definitions

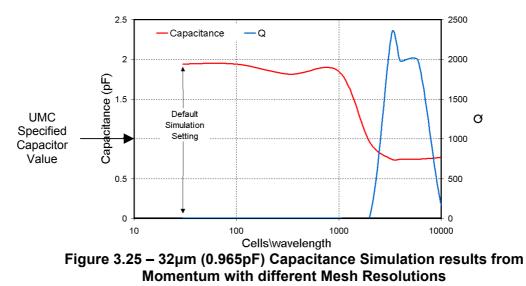

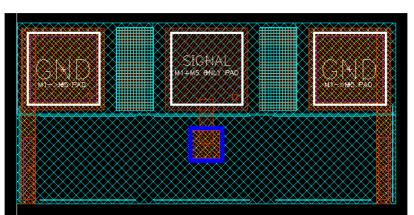

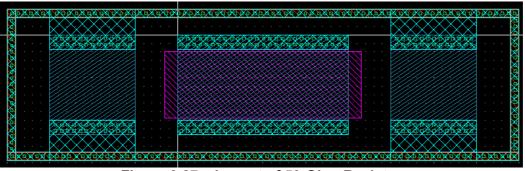

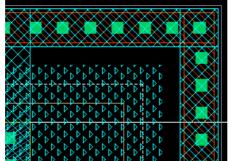

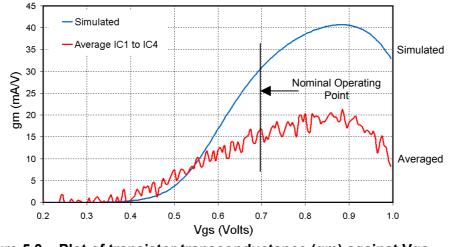

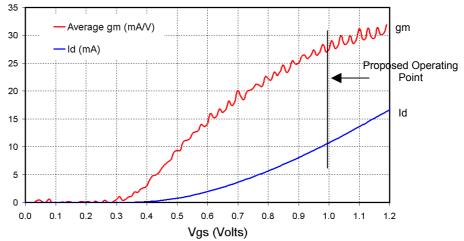

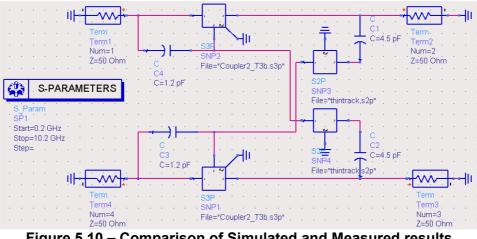

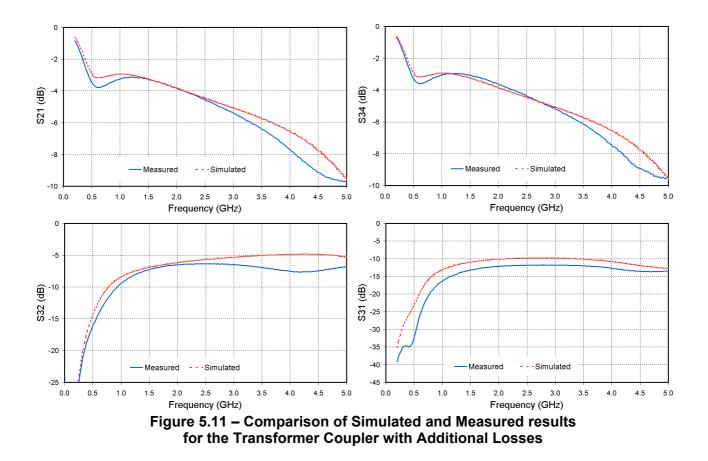

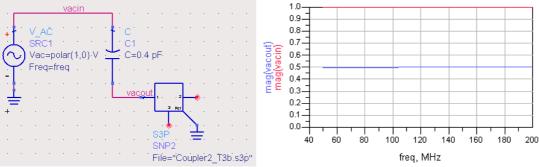

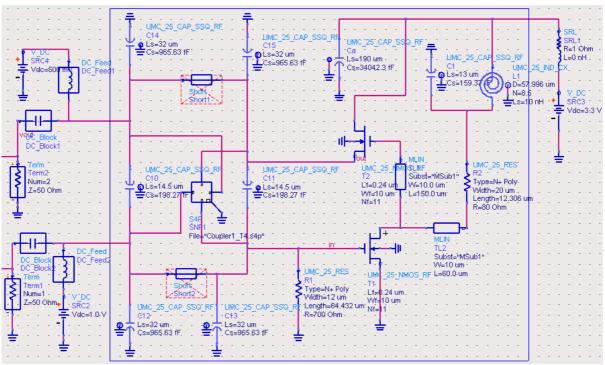

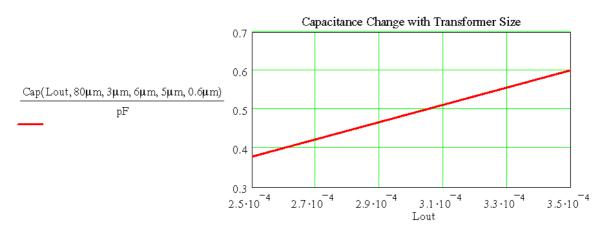

It is possible to achieve an inductor with a higher Q if a multi-sided design had been chosen for the design, for example a spiral, octagon or a hexagon. The rectangle inductor was chosen in preference for a number of reasons. Firstly the simulation time is less, the inductor in Figure 3.2